# **LOGIC**

■ 5304804 0011588 842 ■LLC

L64702 JPEG Coprocessor Technical Manual

July 1993

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified either the functional descriptions, or the electrical and mechanical specifications using production parts.

First Edition

Document Number MD71-000102-99 A

This document applies to revision B of the L64702 and to all subsequent versions unless otherwise indicated in a subsequent edition or an update to this edition of the document.

Publications are stocked at the address given below. Requests should be addressed to:

LSI Logic Corporation Literature Distribution, M/S D-102 1551 McCarthy Boulevard Milpitas, CA 95035 Fax: 408.433.8989

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

© 1993 LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

### **Preface**

This book is the primary reference and user's manual for the L64702 JPEG Coprocessor. It contains a complete functional description for the L64702 and includes complete physical and electrical specifications for the L64702.

#### **Audience**

This book assumes that you have some familiarity with digital signal processing, microprocessors, and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the L64702 JPEG Coprocessor for possible use in a system.

- Engineers who are designing the L64702 into a system.

### Organization

This book has the following chapters:

- Chapter 1, Introduction, defines the general characteristics and capabilities of the L64702.

- Chapter 2, Interface Description, describes the characteristics of the L64702 signals that are used to interface with an external CPU, DMA controller, or video memory.

- Chapter 3, Internal Registers and Data Tables, describes how data is represented inside the L64702. This chapter also provides a summary of the L64702 registers and tables.

- Chapter 4, System Interface, describes the CPU and DMA transfer modes supported by the L64702.

- Chapter 5, JPEG Processing Unit, discusses the role of the L64702 JPEG Coprocessor in image compression and decompression.

- Chapter 6, Compressed Image Data Structure, describes the JPEG file structure and organization for both compressed and decompressed images.

- Chapter 7, Video Memory Organization, describes how the image data is represented in external video memory and describes raster-to-block conversion, image sub-sampling, and color memory organization.

Preface

iii

- Chapter 8, Pixel Data Processing Overview, presents a summary of preand post-processing the L64702 performs on image data. It describes the functions of the Pixel Reformatting Buffer, Color Space Converter, MCU Buffer, and explains level shifting and range limiting.

- Chapter 9, Video Memory Interface Port, describes the interface between the L64702 and an external video memory bus. Included are descriptions of the video bus arbitration protocol, video bus request criteria, and video bus interface timing details.

- Chapter 10, System Interface Port, discusses the interface timing details of CPU and DMA transfers to and from various registers and tables within the L64702.

- Chapter 11, System Software Control, describes how the system software interacts with the L64702 in order to perform L64702 initialization as well as image compression and decompression.

- Chapter 12, **Specifications**, describes the electrical and mechanical characteristics of the L64702.

- Appendix A, The JVieW<sup>TM</sup> (JPEG Video-in-a-Window) Multimedia Kit, describes the JVieW evaluation board, a single-board multimedia design that allows full-motion video to be displayed on a PC.

- Appendix B, Huffman Table Software Listing, describes the source code that generates the Huffman Tables stored in the L64702 RAM.

- Appendix C, Customer Feedback, includes a form that you may use to fax us your comments about this document.

#### Related Publications

JPEG Chipset Technical Manual, Order No. I1400.A

JVieW (JPEG Video in a Window) Evaluation Kit User's Guide, Document No. MD75-000102-99 A

### Conventions Used in this Manual

The first time a word or phrase is defined in this manual, it is italicized.

The following signal naming conventions are used throughout this manual:

- A level-significant signal that is true or valid when the signal is LOW always has an overbar ( ) over its name.

- An edge-significant signal that initiates actions on a HIGH-to-LOW transition always has an overbar ( ) over its name.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by a subscripted "2" following the number—for example, 0011.0010.1110.1111<sub>2</sub>.

### **Contents**

| Chapter 1 | Intro | oduction                                | 1-1  |

|-----------|-------|-----------------------------------------|------|

| •         | 1.1   | Processor and System Overview           | 1-1  |

|           | 1.2   | Features                                | 1-5  |

|           | 1.3   | System Description                      | 1-8  |

|           |       | Coprocessor Configuration               | 1-8  |

|           |       | Stand-Alone Configuration               | 1-10 |

|           |       | Single-Bus Coprocessor Configuration    | 1-11 |

|           | 1.4   | JPEG Image Compression                  | 1-12 |

|           | 1.5   | Standards Compliance                    | 1-13 |

|           |       | CCIR 601 (Mod F)                        | 1-13 |

|           |       | JPEG DIS 10918                          | 1-13 |

|           | 1.6   | Terms and Concepts                      | 1-14 |

|           |       | Minimum Coded Unit (MCU)                | 1-14 |

|           |       | MCU Boundaries                          | 1-17 |

|           |       | Display Active Image Area               | 1-17 |

|           |       | Compressed Image Active Window          | 1-18 |

|           |       | Color Conversion                        | 1-18 |

|           |       | Subsampling                             | 1-19 |

|           |       | Image Reconstruction                    | 1-20 |

|           |       | Raster-to-Block Conversion              | 1-20 |

|           |       | DCT Functions                           | 1-21 |

|           |       | Quantization Function                   | 1-22 |

|           |       | Zigzag Ordering                         | 1-25 |

|           |       | DPCM Coding                             | 1-27 |

|           |       | Run-Length Coding                       | 1-27 |

|           |       | Variable-Length Coding (Huffman Coding) | 1-27 |

|           |       | Encoding Example                        | 1-28 |

|           | 1.7   | Applications                            | 1-30 |

| Chapter 2 | Inte  | rface Description                       | 2-1  |

Contents

### ■ 5304804 0011594 046 ■LLC

|           | 2.1  | System Interface Signals                             | 2-2  |

|-----------|------|------------------------------------------------------|------|

|           | 2.2  | Clock/Reset Interface Signals                        | 2-4  |

|           | 2.3  | Video Memory Interface Signals                       | 2-4  |

|           | 2.4  | Video Bus Arbitration Signals                        | 2-8  |

| Chapter 3 | Inte | rnal Registers and Data Tables                       | 3-1  |

|           | 3.1  | L64702 Register Overview                             | 3-1  |

|           | 3.2  | Group 0 Address Pointer Register (APR)               | 3-3  |

|           | 3.3  | Group 1 Registers                                    | 3-3  |

|           |      | System Mode Register (SMR)                           | 3-3  |

|           |      | System Status Register (STS)                         | 3-8  |

|           | 3.4  | Group 2 Registers and Tables                         | 3-11 |

|           |      | Group 2 Register and Table Summary                   | 3-13 |

|           |      | Huffman Code Tables                                  | 3-14 |

|           |      | System Configuration Register (SCR)                  | 3-15 |

|           |      | JPEG Configuration Register (JCR)                    | 3-19 |

|           |      | Active Height Register (AH)                          | 3-22 |

|           |      | Active Width Register (AW)                           | 3-22 |

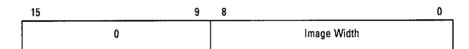

|           |      | Image Width Register (IW)                            | 3-23 |

|           |      | Macro Block Size Register (MBS)                      | 3-25 |

|           |      | Macro Block Size in the Y Direction Register (MBS_Y) | 3-26 |

|           |      | Macro Block Size in the X Direction Register (MBS_X) | 3-28 |

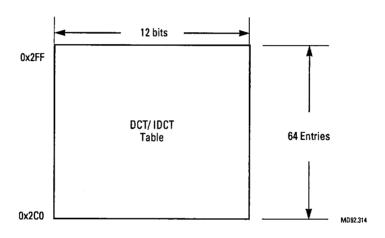

|           |      | DCT/IDCT Factors                                     | 3-30 |

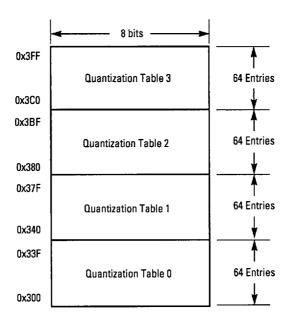

|           |      | Quantization Tables                                  | 3-30 |

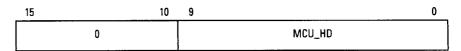

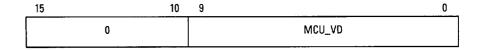

|           |      | MCU Horizontal Delay Register (MCU_HD)               | 3-31 |

|           |      | MCU Vertical Delay Register (MCU_VD)                 | 3-31 |

|           |      | Height/Width Component Registers                     | 3-32 |

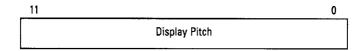

|           |      | Display Pitch Registers                              | 3-34 |

|           |      | Start Address Registers                              | 3-34 |

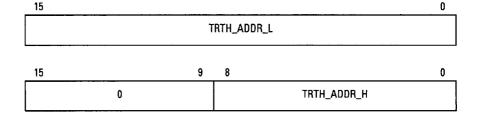

|           |      | Transfer-Through Address Register                    | 3-35 |

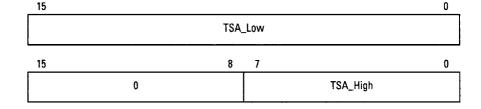

|           |      | Transfer Start Address Register                      | 3-35 |

|           |      | Transfer Increment Register                          | 3-36 |

|           |      | Color Space Conversion Registers (CSC)               | 3-36 |

|           | 3.5  | Group 3 FIFO                                         | 3-37 |

|           | 2.3  | Accessing the FIFO                                   | 3-38 |

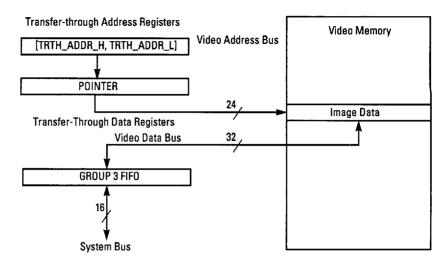

|           |      | Video Memory Transfer-through Mode                   | 3_30 |

| Chapter 4 | Syste | em Interface                                             | 4-1  |

|-----------|-------|----------------------------------------------------------|------|

| onaptor T | 4.1   | CPU and DMA Transfer Mode Overview                       | 4-1  |

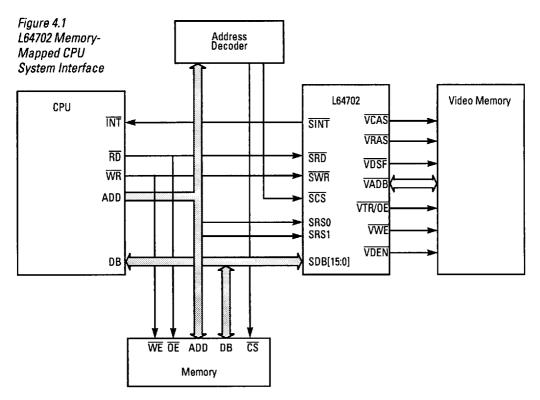

|           | 4.2   | CPU Transfer Mode                                        | 4-3  |

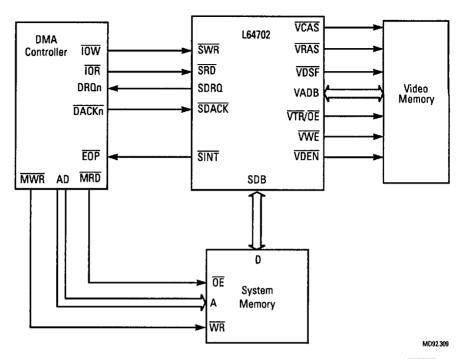

|           | 4.3   | DMA Transfer Mode                                        | 4-5  |

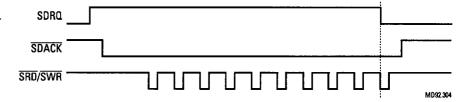

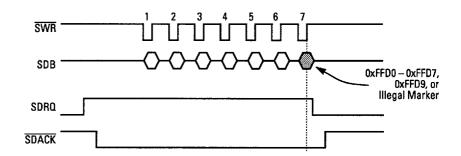

|           |       | Initialization of Group 2 Tables and Registers Using DMA | 4-7  |

|           |       | Reading and Writing the Group 3 FIFO Using DMA           | 4-7  |

| Chapter 5 | JPE   | 3 Processing Unit                                        | 5-1  |

|           | 5.1   | JPU Overview                                             | 5-1  |

|           | 5.2   | FDCT/IDCT Block                                          | 5-3  |

|           | 5.3   | Quantizer/ Inverse Quantizer Block                       | 5-6  |

|           | 5.4   | Zigzag Conversion                                        | 5-7  |

|           | 5.5   | Differential/Inverse Differential Pulse Code Modulation  | 5-8  |

|           | 5.6   | Variable-Length Coding and Decoding (VLC/VLD)            | 5-8  |

| Chapter 6 | Com   | pressed Image Data Structure                             | 6-1  |

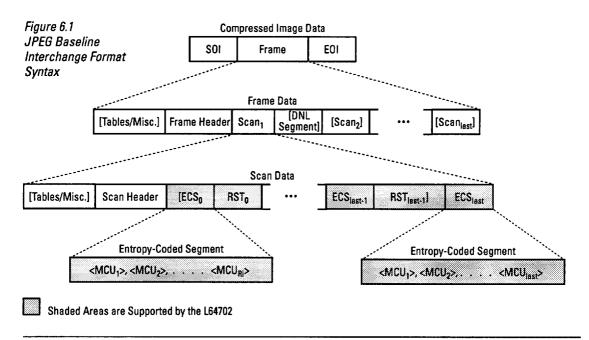

| •         | 6.1   | JPEG Interchange Format                                  | 6-1  |

|           |       | Frame Data                                               | 6-2  |

|           |       | Scan Data                                                | 6-2  |

|           |       | Entropy-Coded Segment (ECS)                              | 6-2  |

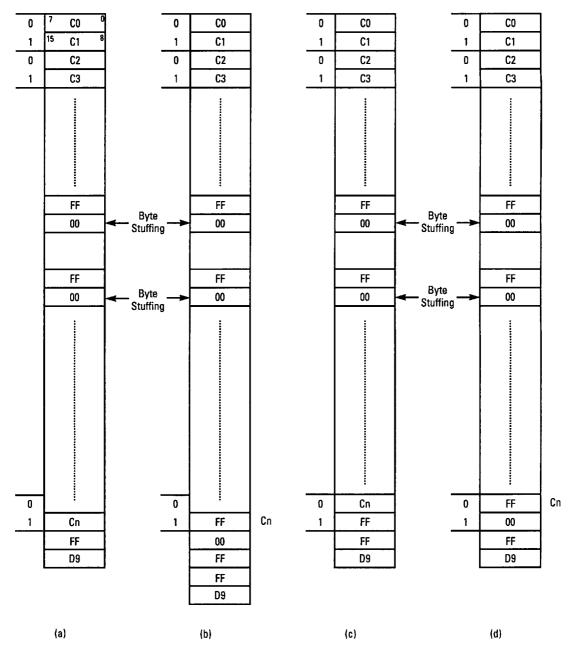

|           | 6.2   | Compressed Data Segments                                 | 6-3  |

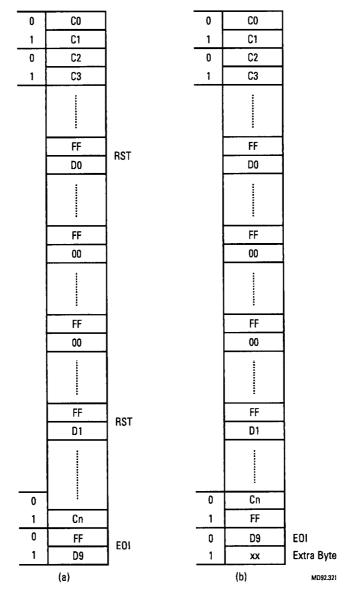

|           | 6.3   | Decompression Code Data Structure                        | 6-5  |

|           |       | Reset Marker Code (RSTm)                                 | 6-6  |

|           |       | End of Image Marker Code (EOI)                           | 6-6  |

|           |       | Other Marker Codes                                       | 6-6  |

| Chapter 7 | Vide  | oo Memory Organization                                   | 7-1  |

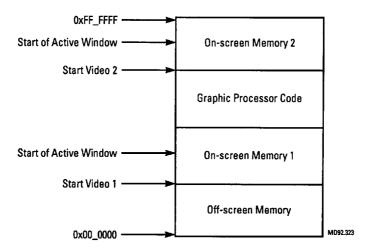

| ·         | 7.1   | Video Memory Address Space                               | 7-1  |

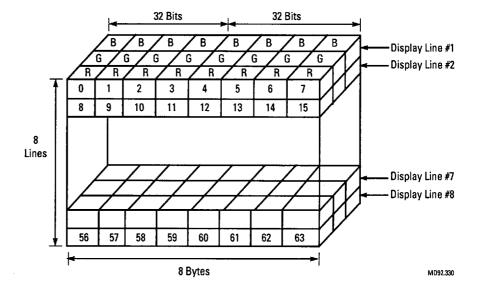

|           | 7.2   | Raster-to-Block Conversion                               | 7-3  |

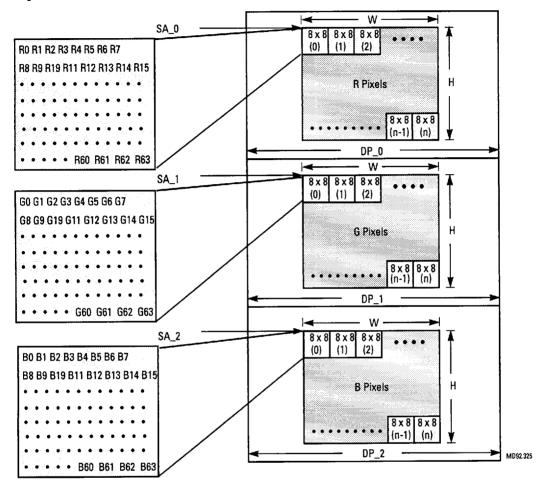

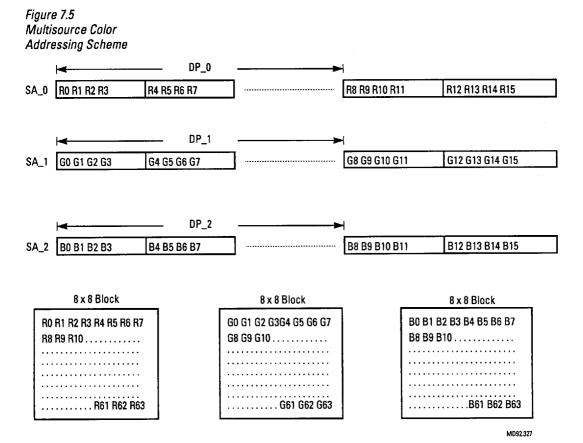

|           | 7.3   | Color Memory Organization                                | 7-3  |

|           |       | Multisource Color Memory Organization                    | 7-4  |

|           |       | Unpacked Color Memory Organization                       | 7-8  |

|           |       | Packed Color Memory Organization                         | 7-12 |

|           |       | Components Sequential Memory Organization                | 7-1: |

|           | 7.4   | Image Subsampling                                        | 7-2  |

|           | 7.5   | Scrolling in Compressed Files                            | 7-2  |

|            | 7.6   | Active Window and Two-Dimensional Addressing      | 7-24 |

|------------|-------|---------------------------------------------------|------|

|            |       | Active Window Start Address                       | 7-25 |

|            |       | Active Window Width                               | 7-26 |

|            |       | Active Window Height                              | 7-27 |

|            |       | Active Height and Width Example                   | 7-29 |

|            |       | Active Window Display Pitch                       | 7-29 |

| Chapter 8  | Pixe  | el Data Processing Overview                       | 8-1  |

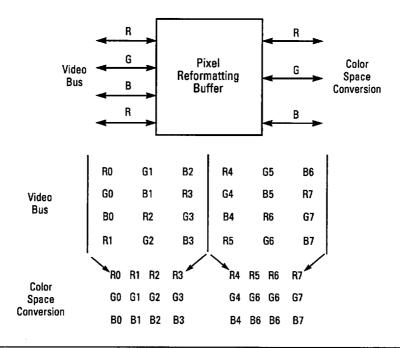

|            | 8.1   | Pixel Data Reformatting Buffer (PRB)              | 8-1  |

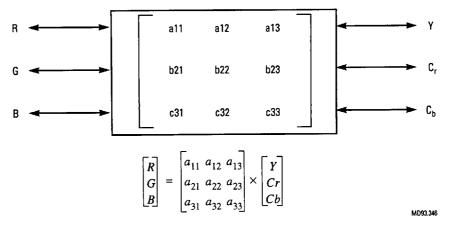

|            | 8.2   | Color Space Converter (CSC)                       | 8-2  |

|            |       | RGB-to-YCbCr                                      | 8-4  |

|            |       | YCbCr-to-RGB                                      | 8-4  |

|            |       | RGB-to-Y (Gray)                                   | 8-5  |

|            |       | Y-to-RGB                                          | 8-5  |

|            |       | Color Space Conversion Bypass                     | 8-5  |

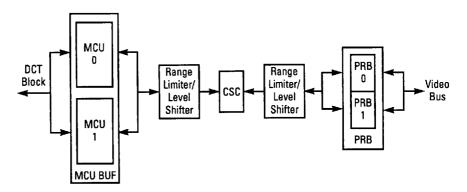

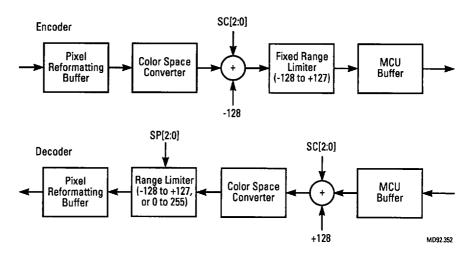

|            | 8.3   | Level Shifting and Range Limiting                 | 8-5  |

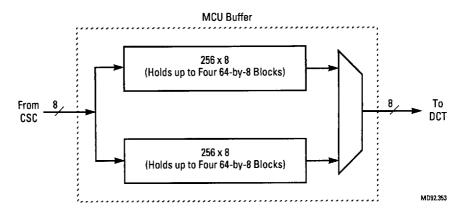

|            | 8.4   | MCU Buffer                                        | 8-6  |

| Chapter 9  | Vide  | o Memory Interface Port                           | 9-1  |

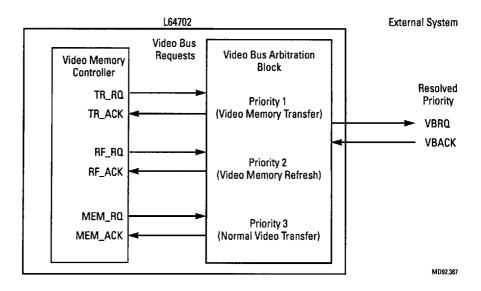

|            | 9.1   | Video Bus Arbitration Protocol                    | 9-1  |

|            | 9.2   | Video Bus Request Criteria and Priorities         | 9-3  |

|            |       | Video Memory Transfer Request Criteria            | 9-4  |

|            |       | Video Memory Refresh Request Criteria             | 9-4  |

|            |       | Video Memory Read or Write Cycle Request Criteria | 9-4  |

|            | 9.3   | Video Bus Interface Timing                        | 9-5  |

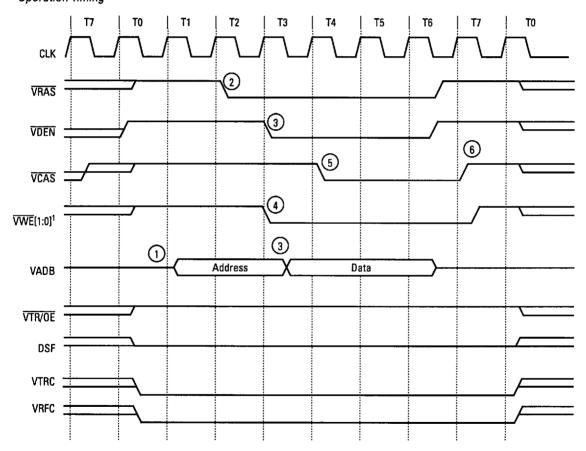

|            |       | VRAM Serial Port Control                          | 9-9  |

|            |       | Video Memory Early Write Cycle                    | 9-11 |

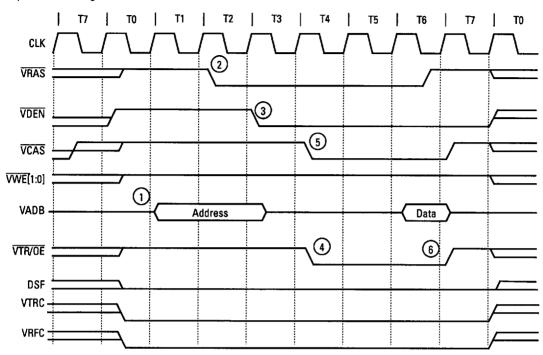

|            |       | Video Memory Read Cycle                           | 9-13 |

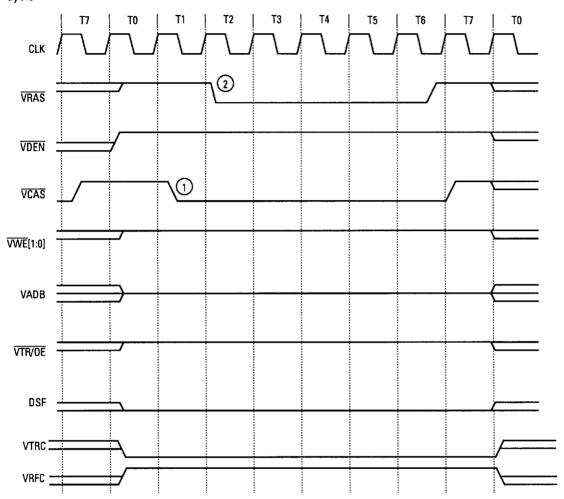

|            |       | CAS-before-RAS Video Memory Refresh Cycle         | 9-14 |

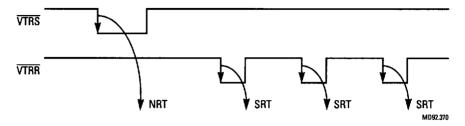

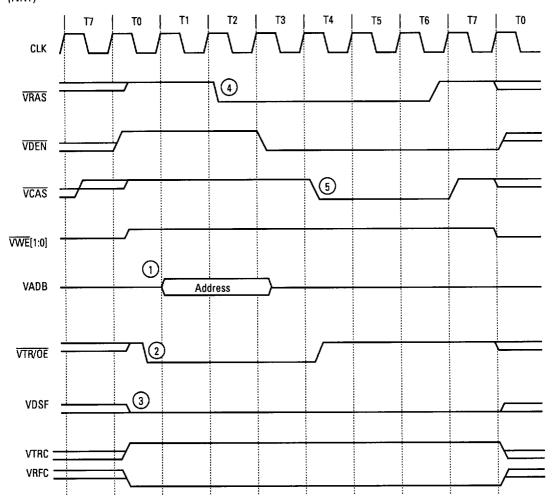

|            |       | Normal Read Transfer Cycle DRAM-TO-SAM (NRT)      | 9-16 |

|            |       | Split Read Transfer Cycle DRAM-to-SAM (SRT)       | 9-18 |

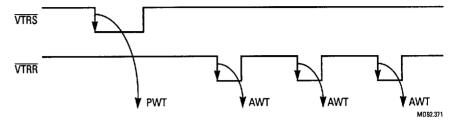

|            |       | Pseudo-Write Transfer Cycle (PWT)                 | 9-20 |

|            |       | Alternate Write Transfer SAM-to-DRAM (AWT)        | 9-22 |

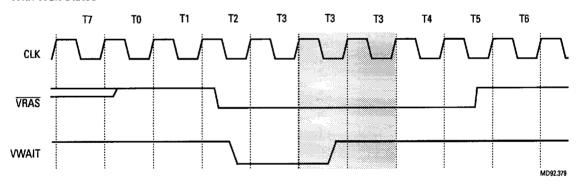

|            |       | Video Memory Cycle with Wait States               | 9-24 |

| Chapter 10 | Syste | em Interface Port                                 | 10-1 |

|            | 10.1  | CPU Transfer Mode                                 | 10-1 |

|            |       | CPU Write to the Address Pointer Register (APR)   | 10-2 |

|            |       | CPU Read from the Address Pointer Register (APR)  | 10-2 |

|            | CPU Read from the Status Register (STS)           | 10-4         |

|------------|---------------------------------------------------|--------------|

|            | CPU Write to the System Mode Register (SMR)       | 10-5         |

|            | CPU Read from the Registers and Tables            | 10-6         |

|            | CPU Write to the Registers and Tables             | 10-7         |

|            | CPU Read from the FIFO                            | 10-8         |

|            | CPU Write to the FIFO                             | 10-9         |

|            | 10.2 DMA Transfer Mode                            | 10-10        |

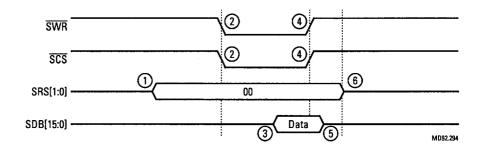

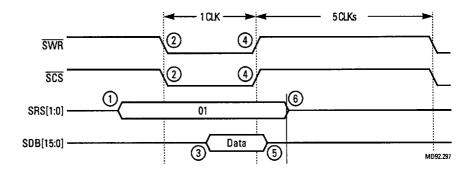

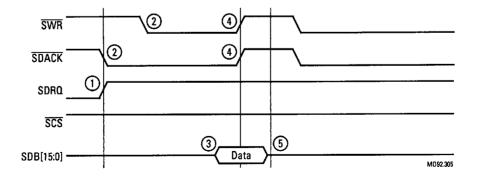

|            | DMA Write Operation                               | 10-10        |

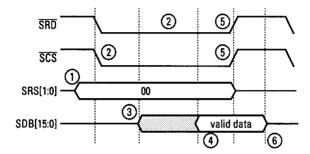

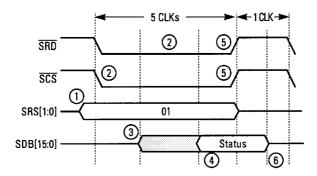

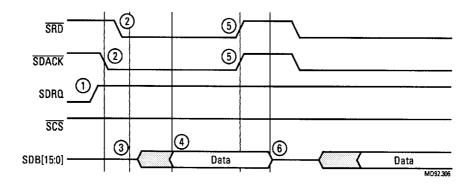

|            | DMA Read Operation                                | 10-11        |

| Chapter 11 | System Software Control                           | 11-1         |

| -          | 11.1 Initialization Task                          | 11-1         |

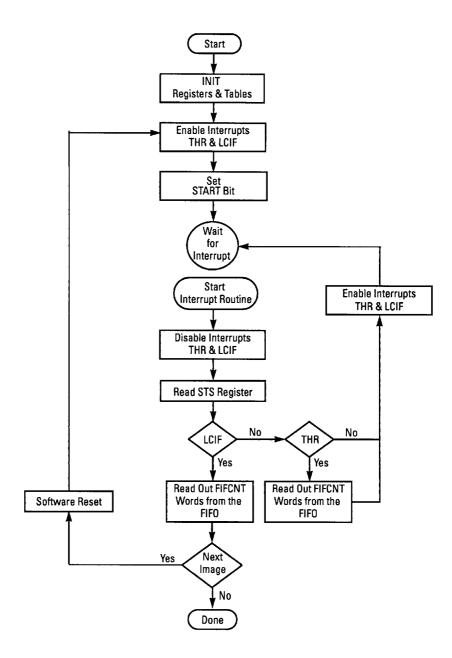

|            | 11.2 Image Compression Task                       | 11-2         |

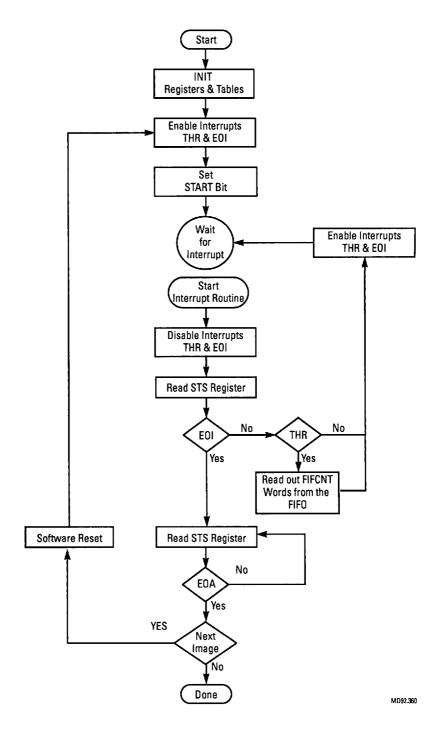

|            | 11.3 Image Decompression Task                     | 11-4         |

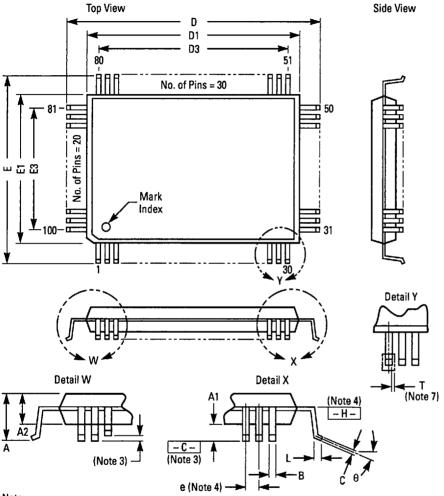

| Chapter 12 | Specifications                                    | 12-1         |

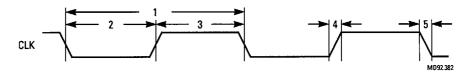

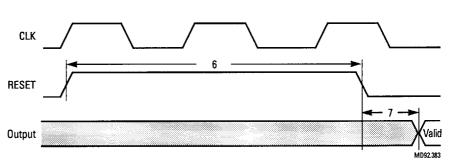

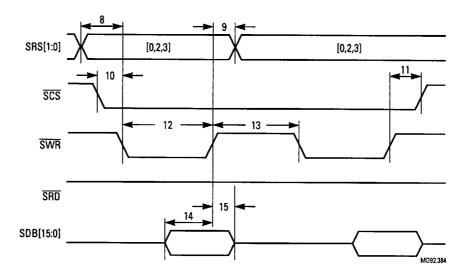

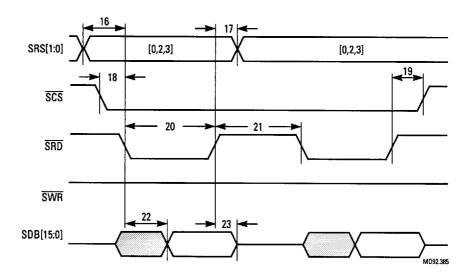

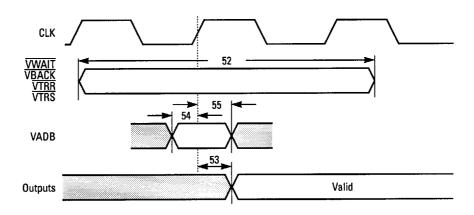

|            | 12.1 AC Timing                                    | 12-1         |

|            | CLK and RESET Timing                              | 12-4         |

|            | System Port Timing                                | 12-4         |

|            | Video Port Timing                                 | 12-7         |

|            | 12.2 Electrical Requirements                      | 12-8         |

|            | 12.3 Packaging                                    | 12-11        |

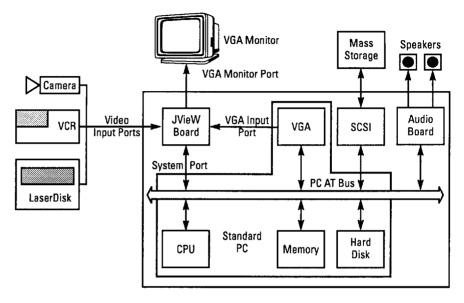

| Appendix A | The JVieW (JPEG Video in a Window) Evaluation Kit | A-1          |

|            | A.1 Overview                                      | A-1          |

|            | A.2 Kit Contents                                  | A-2          |

|            | A.3 System Requirements                           | A-2          |

|            | A.4 Features Summary                              | A-3          |

|            | A.5 JVieW Board in a Multimedia PC System         | A-3          |

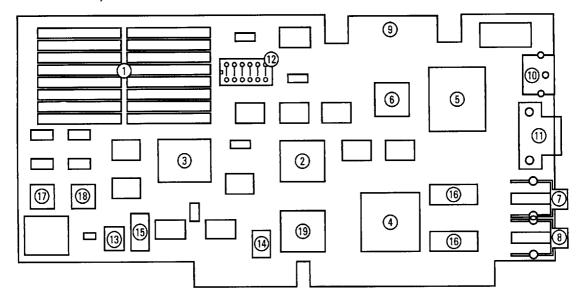

|            | A.6 JVieW Board Layout                            | A-5          |

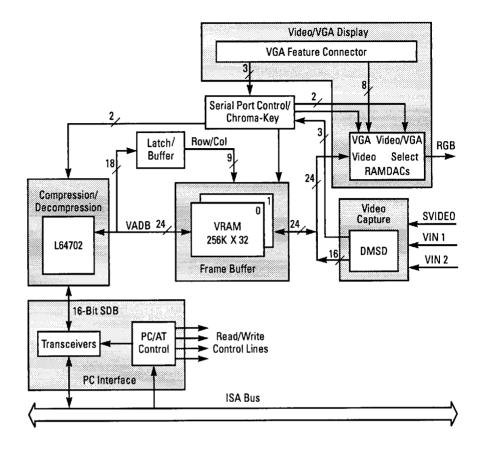

|            | A.7 JVieW Board Functional Description            | A-6          |

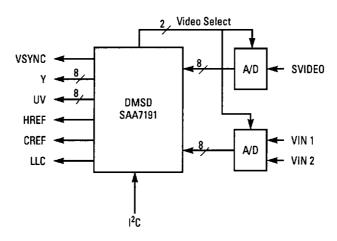

|            | Video Capture                                     | A-7          |

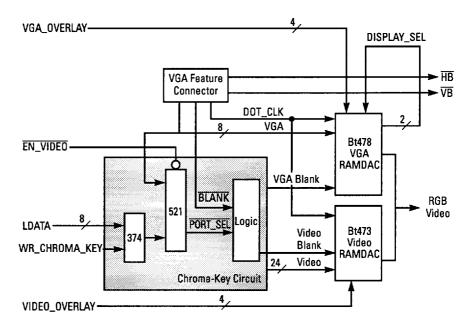

|            | Video/VGA Display                                 | A-8          |

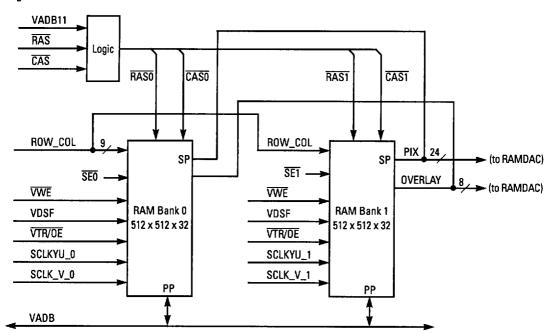

|            | Frame Buffer                                      | A-9          |

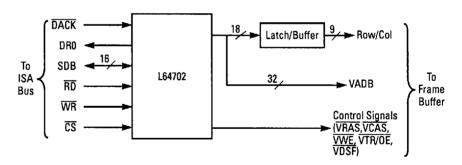

|            | Compression/ Decompression                        | <b>A-1</b> 1 |

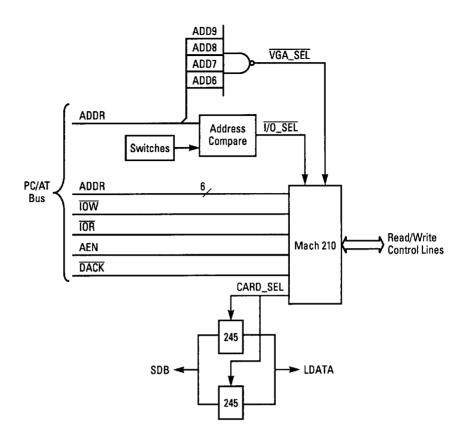

|            | PC Interface                                      | <b>A-1</b> 1 |

| Appendix B | Huffman Table Software Listing                    | В-:          |

| Appendix C | Cust | omer Feedback                                         | C-1  |

|------------|------|-------------------------------------------------------|------|

| Figures    | 1.1  | L64702 General Block Diagram                          | 1-2  |

|            | 1.2  | L64702 Detailed Block Diagram                         | 1-3  |

|            | 1.3  | File Interchange in a Microcomputer System            | 1-8  |

|            | 1.4  | Coprocessor System Configuration                      | 1-9  |

|            | 1.5  | Stand-Alone System                                    | 1-11 |

|            | 1.6  | Single-Bus Coprocessor Configuration                  | 1-12 |

|            | 1.7  | Construction of an MCU from Three Color Components    | 1-15 |

|            | 1.8  | Construction of an MCU from Four Color Components     | 1-16 |

|            | 1.9  | Active Image Area                                     | 1-17 |

|            | 1.10 | Compressed Image Active Window                        | 1-18 |

|            | 1.11 | Image Reconstruction from YCrCb to RGB                | 1-20 |

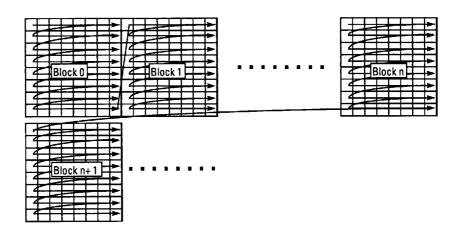

|            | 1.12 | Raster-to-Block Conversion                            | 1-21 |

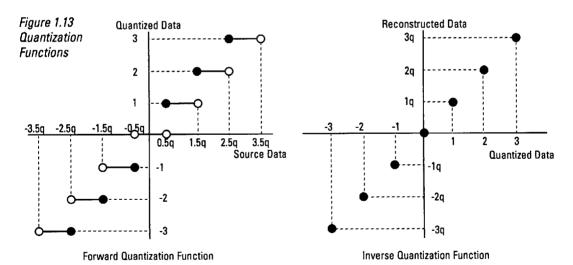

|            | 1.13 | Quantization Functions                                | 1-23 |

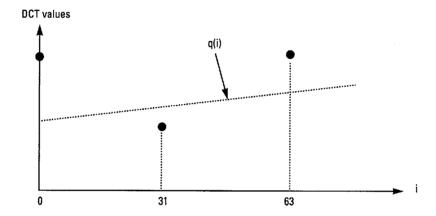

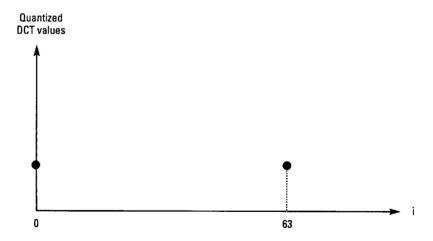

|            | 1.14 | Quantization Example                                  | 1-24 |

|            | 1.15 | Zigzag Ordering                                       | 1-25 |

|            | 1.16 | Raster and Zigzag Encoding Example                    | 1-26 |

|            | 1.17 | Encoding Example                                      | 1-28 |

|            | 1.18 | Codeword Structure                                    | 1-30 |

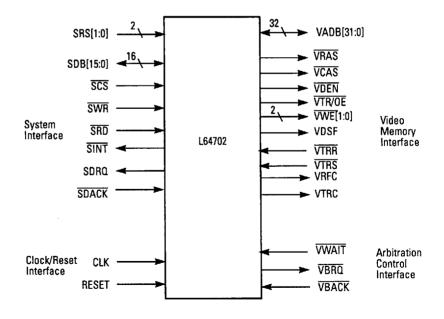

|            | 2.1  | L64702 Logic Symbol                                   | 2-1  |

|            | 3.1  | Address Pointer Register                              | 3-3  |

|            | 3.2  | System Mode Register                                  | 3-3  |

|            | 3.3  | System Status Register                                | 3-8  |

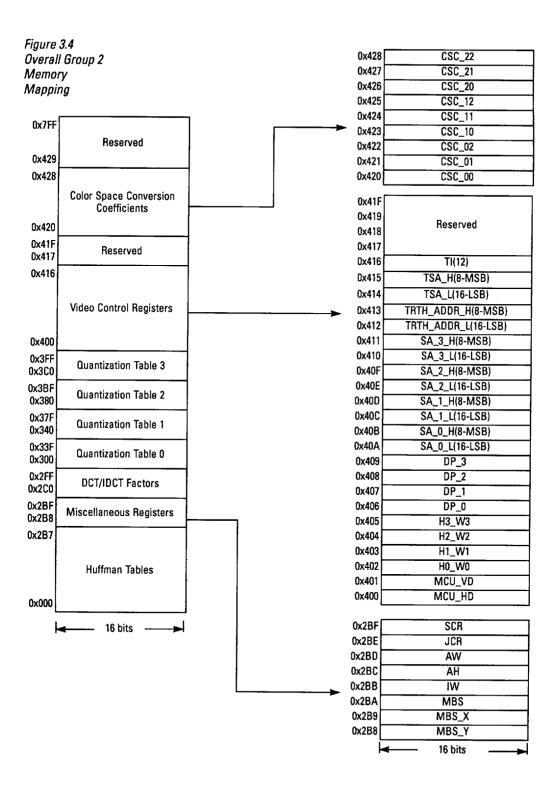

|            | 3.4  | Overall Group 2 Memory Mapping                        | 3-12 |

|            | 3.5  | System Configuration Register                         | 3-15 |

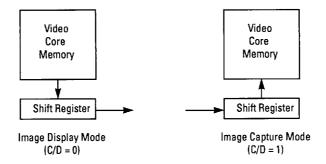

|            | 3.6  | Image Capture and Display Modes                       | 3-17 |

|            | 3.7  | JPEG Configuration Register (JCR)                     | 3-19 |

|            | 3.8  | Active Height Register (AH)                           | 3-22 |

|            | 3.9  | Active Image Area                                     | 3-24 |

|            | 3.10 | Display Pitch                                         | 3-24 |

|            | 3.11 | Starting Address                                      | 3-24 |

|            | 3.12 | Macro Block Size Register (MBS)                       | 3-25 |

|            | 3.13 | DCT/IDCT Table                                        | 3-30 |

|            | 3.14 | Quantization Tables                                   | 3-31 |

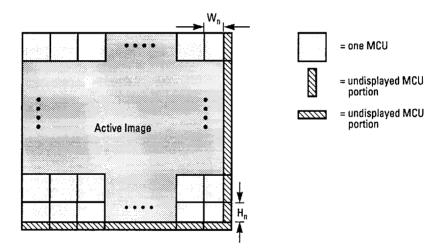

|            | 3.15 | W <sub>n</sub> and H <sub>n</sub> in the Active Image | 3-32 |

|            | 3.16 | SA_0 LOW and HIGH Registers                           | 3-34 |

|            | 3.17 | SA_1 LOW and HIGH Registers                           | 3-34 |

|            |      | _                                                     | -    |

| 3.18 | SA_2 LOW and HIGH Registers                              | 3-34 |

|------|----------------------------------------------------------|------|

| 3.19 | SA_3 LOW and HIGH Registers                              | 3-35 |

| 3.20 | TRTH_ADDR Register                                       | 3-35 |

| 3.21 | TSA Register                                             | 3-35 |

| 3.22 | Video Memory Transfer-Through Mode                       | 3-40 |

| 4.1  | L64702 Memory-Mapped CPU System Interface                | 4-3  |

| 4.2  | DMA Transfer Configuration                               | 4-6  |

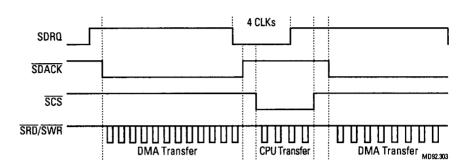

| 4.3  | DMA Burst Transfer Timing                                | 4-8  |

| 4.4  | DMA Burst Transfer Timing with EOI, RI, or IMC Condition | 4-8  |

| 4.5  | DMA Transfer Protocol                                    | 4-9  |

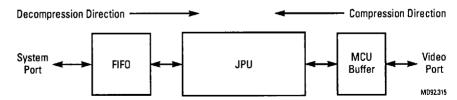

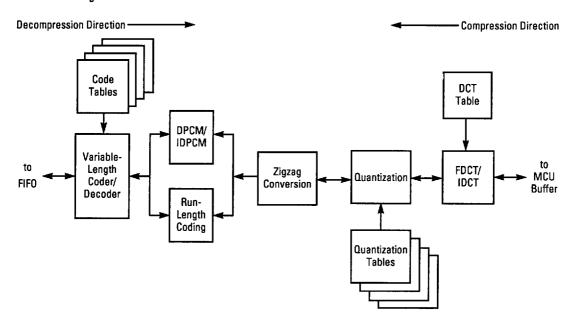

| 5.1  | JPEG Image Processing Operations                         | 5-1  |

| 5.2  | JPEG Processing Unit Block Diagram                       | 5-2  |

| 5.3  | FDCT and IDCT Factors                                    | 5-5  |

| 5.4  | Luminance and Chrominance Quantization Tables            | 5-7  |

| 5.5  | Zigzag Sequence of Quantized DCT Coefficients            | 5-7  |

| 6.1  | JPEG Baseline Interchange Format Syntax                  | 6-2  |

| 6.2  | L64702-created Code Data Streams                         | 6-4  |

| 6.3  | Compressed Data Structures Supplied to L64702            | 6-7  |

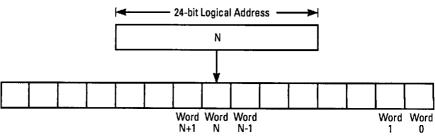

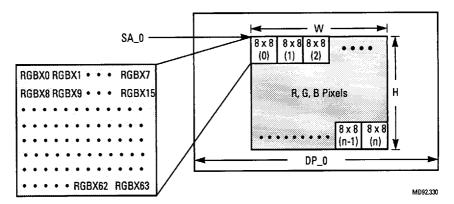

| 7.1  | Logical Memory Address Space                             | 7-2  |

| 7.2  | Physical Memory Organization                             | 7-2  |

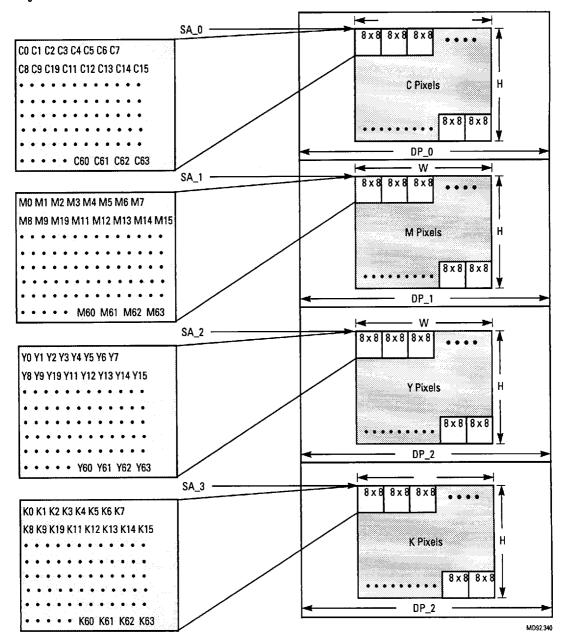

| 7.3  | Multisource Color Memory Organization                    | 7-5  |

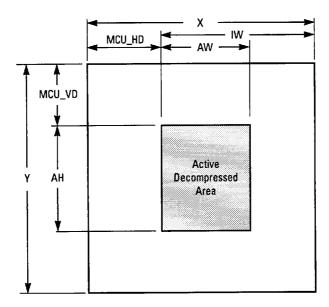

| 7.4  | Multisource Color Video Bus Activity                     | 7-6  |

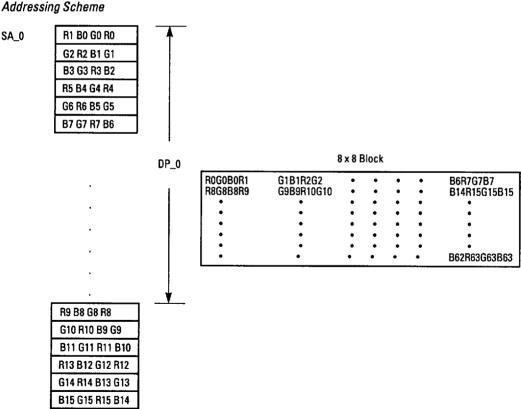

| 7.5  | Multisource Color Addressing Scheme                      | 7-7  |

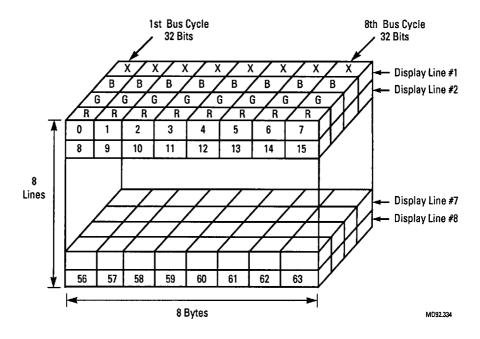

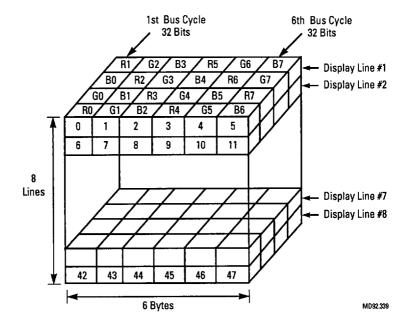

| 7.6  | Three-dimensional 8 x 8 Multisource Display Image        | 7-8  |

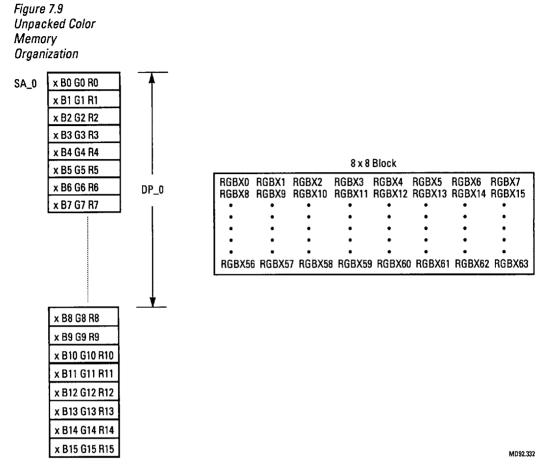

| 7.7  | Unpacked Color Memory Organization                       | 7-9  |

| 7.8  | Unpacked Color Video Bus Activity                        | 7-10 |

| 7.9  | Unpacked Color Memory Organization                       | 7-11 |

| 7.10 | Three-dimensional 8 x 8 Unpacked Display Image           | 7-12 |

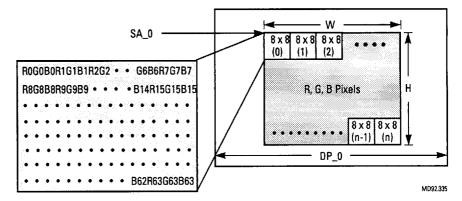

| 7.11 | Packed Color Memory Organization                         | 7-13 |

| 7.12 | Packed Color Video Bus Activity                          | 7-13 |

| 7.13 | Packed Color Addressing Scheme                           | 7-14 |

| 7.14 | Three-dimensional 8 x 8 Packed Display Image             | 7-15 |

| 7.15 | Components Sequential Memory Organization                | 7-17 |

| 7.16 | Components Sequential Addressing Scheme                  | 7-19 |

| 7.17 | Components Sequential Video Bus Activity                 | 7-20 |

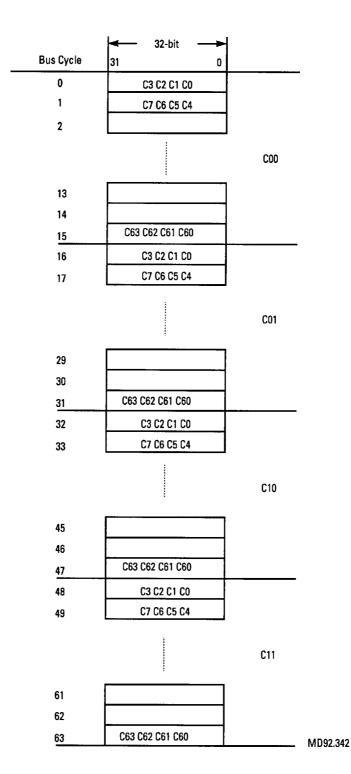

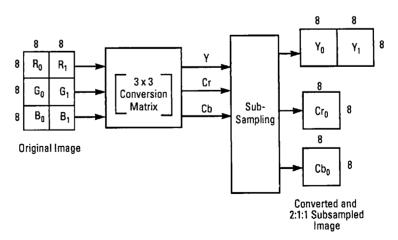

| 7.18 | Color Conversion and Subsampling from RGB to YCrCb       | 7-21 |

| 7.19 | Color Conversion and Subsampling from RGB to Y           | 7-22 |

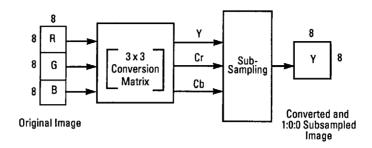

| 7.20 | Active Decompressed Area Inside of a Compressed Image    | 7-23 |

| 7.21 | L64702 Active Window Area and 2-D Addressing Scheme      | 7-25 |

Contents xiii

| 8.1   | Pixel Data Processing Block Diagram               | 8-1   |

|-------|---------------------------------------------------|-------|

| 8.2   | Pixel Data Reformatting Concept                   | 8-2   |

| 8.3   | Color Space Conversion Unit                       | 8-3   |

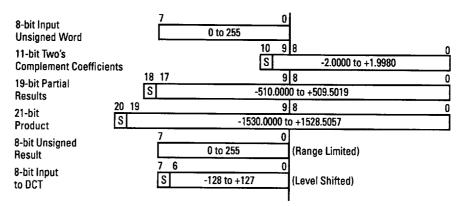

| 8.4   | Color Space Conversion for Unsigned Numbers       | 8-4   |

| 8.5   | Range Limiters and Level Shifter                  | 8-6   |

| 8.6   | MCU Buffer Configuration                          | 8-7   |

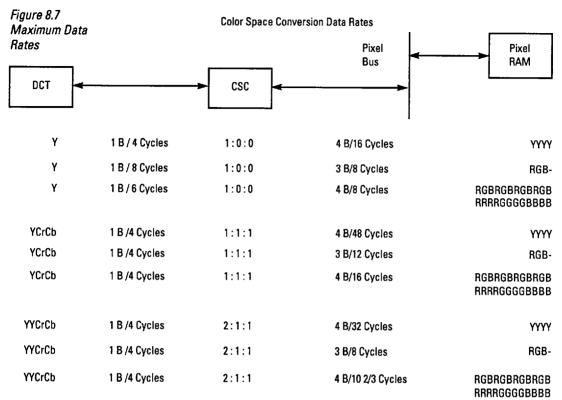

| 8.7   | Maximum Data Rates                                | 8-8   |

| 8.8   | MCU Boundary Schemes                              | 8-9   |

| 9.1   | Regular Video Bus Arbitration Protocol            | 9-2   |

| 9.2   | Video Bus Arbitration Preemption Protocol         | 9-3   |

| 9.3   | Video Bus Internal Arbitration Block              | 9-4   |

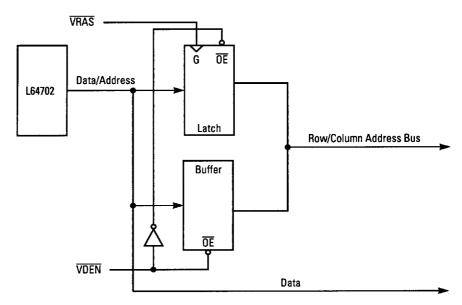

| 9.4   | Typical Row/Column Address Multiplexing Circuitry | 9-6   |

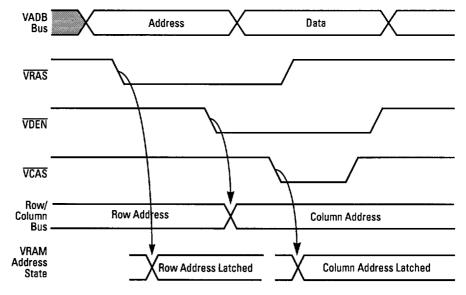

| 9.5   | Row and Column Address Phases of Memory Cycle     | 9-8   |

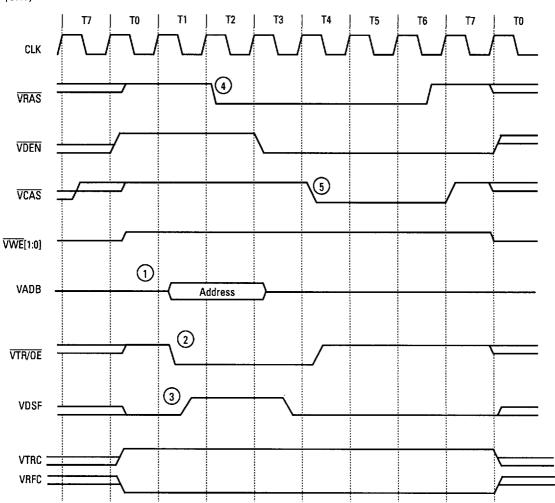

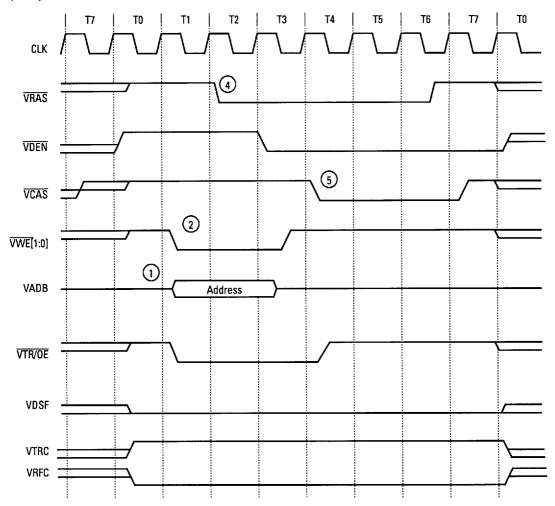

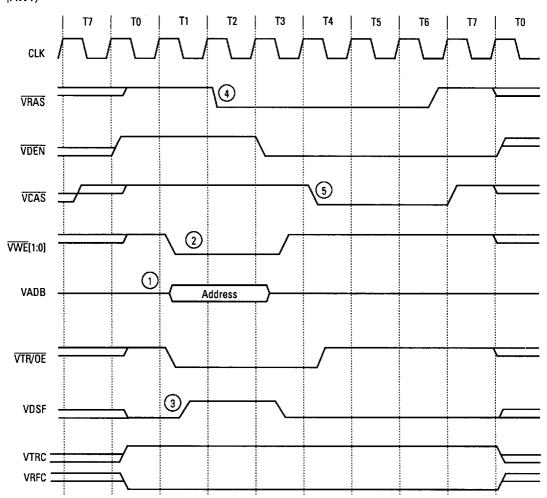

| 9.6   | Display Mode Serial Control Timing                | 9-10  |

| 9.7   | Capture Mode Serial Control Timing                | 9-11  |

| 9.8   | Video-Memory, Early-Write Operation Timing        | 9-12  |

| 9.9   | Video Memory Read Operation Timing                | 9-14  |

| 9.10  | CAS-before-RAS Memory Refresh Cycle               | 9-15  |

| 9.11  | Normal Read Transfer Cycle DRAM-to-SAM (NRT)      | 9-17  |

| 9.12  | Split Read Transfer Cycle DRAM-to-SAM (SRT)       | 9-19  |

| 9.13  | Pseudo Write Transfer Cycle (PWT)                 | 9-21  |

| 9.14  | Alternate Write Transfer Cycle (AWT)              | 9-23  |

| 9.15  | Video Memory Cycle With Wait States               | 9-24  |

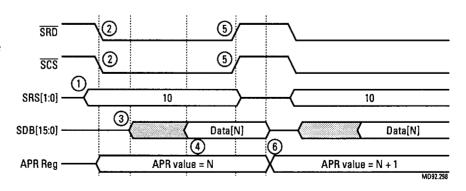

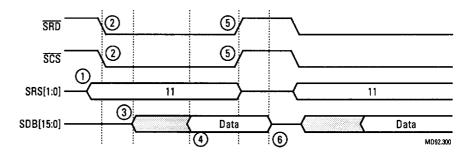

| 10.1  | CPU Write to the APR Register                     | 10-2  |

| 10.2  | CPU Read from the APR Register                    | 10-3  |

| 10.3  | CPU Read from the STS Register                    | 10-4  |

| 10.4  | CPU Write to the SMR Register                     | 10-5  |

| 10.5  | CPU Read from the Registers and Tables            | 10-6  |

| 10.6  | CPU Write to the Registers and Tables             | 10-7  |

| 10.7  | CPU Read from the FIFO                            | 10-8  |

| 10.8  | CPU Write to the FIFO                             | 10-9  |

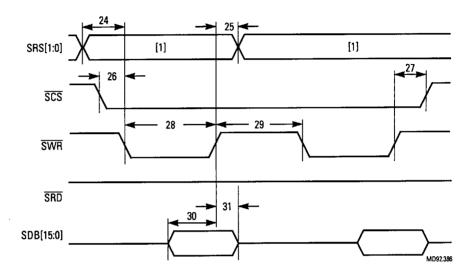

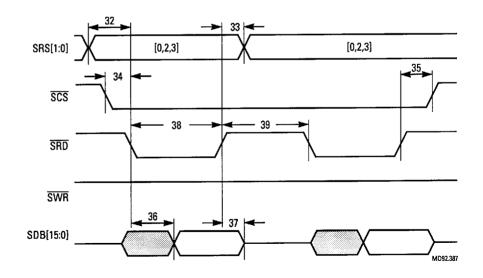

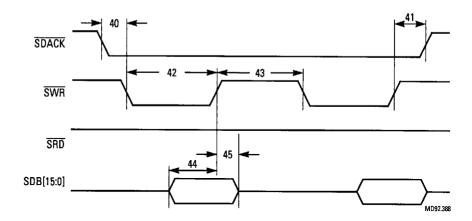

| 10.9  | DMA Write Cycle Timing                            | 10-10 |

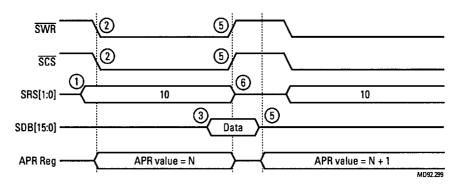

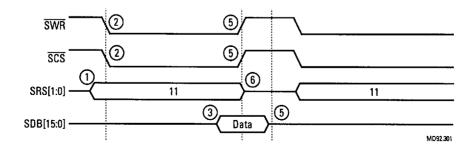

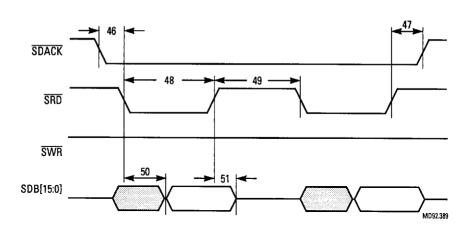

| 10.10 | DMA Read Cycle Timing                             | 10-11 |

| 11.1  | Compression Program Flow Example                  | 11-3  |

| 11.2  | Decompression Program Flow Example                | 11-5  |

| 12.1  | L64702 CLK Timing                                 | 12-4  |

| 12.2  | L64702 RESET Timing                               | 12-4  |

| 12.3  | CPU Write Cycle Timing                            | 12-5  |

### ■ 5304804 0011601 006 **■**LLC

|        | 12.4  | CPU Read Cycle Timing                                       | 12-5  |

|--------|-------|-------------------------------------------------------------|-------|

|        | 12.5  | CPU Write Cycle to the SMR Register                         | 12-6  |

|        | 12.6  | CPU Read Cycle from the STS Register                        | 12-6  |

|        | 12.7  | DMA Write Cycle Timing                                      | 12-7  |

|        | 12.8  | DMA Read Cycle Timing                                       | 12-7  |

|        | 12.9  | Video Port Timing                                           | 12-8  |

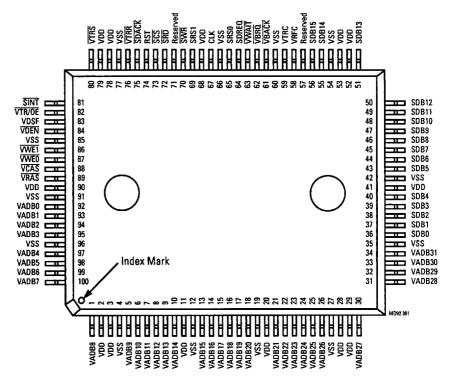

|        | 12.10 | 100-Pin PQFP Pinout                                         | 12-13 |

|        | 12.11 | 100-Pin PQFP Mechanical Drawing                             | 12-14 |

|        | A.1   | PC Multimedia System with JVieW Board                       | A-4   |

|        | A.2   | JVieW Board Layout                                          | A-5   |

|        | A.3   | JVieW Hardware Block Diagram                                | A-7   |

|        | A.4   | Video Capture                                               | A-8   |

|        | A.5   | Video/VGA Display with Chroma-Key                           | A-8   |

|        | A.6   | Frame Buffer Block Diagram                                  | A-10  |

|        | A.7   | L64702 Compression/Decompression                            | A-11  |

|        | A.8   | PC ISA Bus Interface                                        | A-12  |

| Tables | 1.1   | Quantization Examples                                       | 1-24  |

|        | 1.2   | AC Coefficient Size Table                                   | 1-29  |

|        | 1.3   | Sample AC Code Table                                        | 1-29  |

|        | 3.1   | Accessing the L64702 Internal Groups                        | 3-2   |

|        | 3.2   | Group 2 Registers and Tables Summary                        | 3-13  |

|        | 3.3   | Huffman Tables                                              | 3-14  |

|        | 3.4   | W <sub>n</sub> Values                                       | 3-33  |

|        | 3.5   | H <sub>n</sub> Values                                       | 3-33  |

|        | 3.6   | Color Space Conversion Registers                            | 3-36  |

|        | 4.1   | Accessing the L64702 Internal Groups                        | 4-2   |

|        | 7.1   | IDS Field Encoding                                          | 7-4   |

|        | 7.2   | Number of Display Pixels or Words                           | 7-27  |

|        | 7.3   | Number of Display Lines                                     | 7-28  |

|        | 7.4   | W <sub>n</sub> and AW Values for the Color Modes            | 7-29  |

|        | 7.5   | W <sub>n</sub> and AW Values for Components Sequential Mode | 7-29  |

|        | 7.6   | H <sub>n</sub> and AH Values for Components Sequential Mode | 7-29  |

|        | 9.1   | VRAM/DRAM Control Truth Table                               | 9-7   |

|        | 9.2   | SRT Example                                                 | 9-10  |

|        | 9.3   | AWT Example                                                 | 9-11  |

|        | 12.1  | AC Timing Values                                            | 12-2  |

Contents

χV

### 5304804 0011602 T42 BLLC

|          | 12.2 | Absolute Maximum Ratings                   | 12-8  |

|----------|------|--------------------------------------------|-------|

|          | 12.3 | Recommended Operating Conditions           | 12-8  |

|          | 12.4 | Capacitance                                | 12-8  |

|          | 12.5 | DC Characteristics                         | 12-9  |

|          | 12.6 | Pin Description Summary                    | 12-10 |

|          | 12.7 | L64702 Ordering Information                | 12-11 |

|          | 12.8 | Alphabetical Pin List for the 100-pin PQFP | 12-12 |

| quations | 1.1  | RGB to YCrCb Conversion                    | 1-19  |

|          | 1.2  | YCrCb to RGB Conversion                    | 1-19  |

|          | 1.3  | Forward DCT                                | 1-21  |

|          | 1.4  | Inverse DCT                                | 1-21  |

| •        | 1.5  | Forward Quantization                       | 1-22  |

|          | 1.6  | Inverse Quantization                       | 1-22  |

|          | 1.7  | DPCM Coding                                | 1-27  |

|          | 1.8  | DCT Coefficient Calculation                | 1-28  |

|          | 3.1  | Active Height Calculation                  | 3-22  |

|          | 3.2  | Active Width Calculation                   | 3-23  |

|          | 5.1  | Forward Discrete Cosine Transforms         | 5-3   |

|          | 5.2  | Inverse Discrete Cosine Transforms         | 5-3   |

|          | 5.3  | First Step in Calculation                  | 5-4   |

|          | 5.4  | Second Step in Calculation                 | 5-4   |

|          | 5.5  | Quantization and Inverse Quantization      | 5-6   |

|          | 5.6  | DC Difference                              | 5-8   |

|          | 5.7  | DC Term Reconstruction                     | 5-8   |

|          | 7.1  | Horizontal Scrolling                       | 7-23  |

|          | 7.2  | Vertical Scrolling                         | 7-23  |

|          | 7.3  | Active Width Calculation                   | 7-26  |

|          | 7.4  | W0 Calculation                             | 7-26  |

|          | 7.5  | Active Height Calculation                  | 7-27  |

|          | 7.6  | H0 Calculation                             | 7-27  |

|          | 8.1  | RGB-to-YCrCb                               | 8-4   |

|          | 8.2  | YCrCb-to-RGB                               | 8-4   |

|          | 8.3  | Y-to-RGB                                   | 8-5   |

|          | 8.4  | Color Space Conversion Bypass              | 8-5   |

# Chapter 1 Introduction

This document describes the system interface and the architecture specification of the L64702 JPEG Coprocessor, and contains the following sections:

- Section 1.1, Processor and System Overview

- Section 1.2, Features

- Section 1.3, System Description

- Section 1.4, JPEG Image Compression

- Section 1.5, Standards Compliance

- Section 1.6, Terms and Concepts

- Section 1.7, Applications

### 1.1 Processor and System Overview

The L64702 is a single-chip JPEG coprocessor designed for microcomputer graphics and video applications including personal computers, engineering workstations, true-color display cards and monitors, and color laser printers. The L64702's advanced software and hardware interfaces make applications and system-level programming efficient and straightforward. Its performance and high integration make the L64702 a cost-effective component while improving substantially the performance over any system that uses general-purpose DSP devices for JPEG image compression or decompression tasks.

The L64702 is designed to support several image formats dedicated to specific needs within the microcomputer environment. The high-level system approach uses image compression to reduce storage capacity needs and eliminate data transfer bottlenecks over the system bus. Using the JPEG standard for file compression can achieve these benefits while preserving excellent reproduction results.

The L64702 is a half-duplex device, meaning that it can support either image compression or image decompression at one time. The L64702 complies with the latest JPEG baseline recommendation standard (JPEG DIS 10918). Byte stuffing, byte stripping, and restart marker codes are supported. In addition, the device provides user-programmable DCT coefficients, as well as color-space and format conversion capabilities, making the device a flexible and simple solution for image compression and decompression tasks.

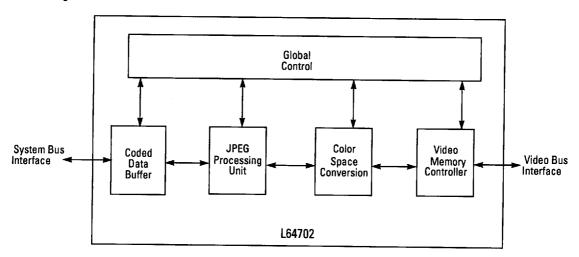

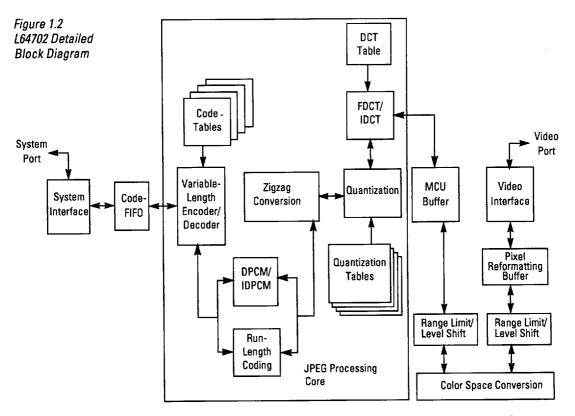

Figure 1.1 is a general block diagram of the L64702, and Figure 1.2 is a more detailed block diagram.

Figure 1.1 L64702 General Block Diagram

The main blocks in the L64702 that comprise the JPEG processing core are:

- 8 x 8 FDCT/IDCT

- Quantization

- DPCM/IDPCM, Run Length Coding, Zigzag Conversion

- Variable Length Encoder/Decoder

The JPEG processing core communicates with two independent interfaces, the video port and the system port. The JPEG processing unit adjusts the processing rate to the bus activity on both sides and temporarily suspends processing when needed with no risk of data stream breakdown. This capability is extremely important for a device that operates in a CPU environment where data and tasks are changing randomly. The System and Video Interfaces allow simple, straight-forward connection of the L64702 to the system bus on one side and video memory on the other side.

On the video port side, the L64702 buffers image data in one of two Minimum Code Unit (MCU) buffers. Each MCU buffer is 256 bytes deep and operates in a ping-pong fashion. While one MCU buffer is transferring data to or from the JPEG processing core, the other MCU buffer is transferring image data to or from external video memory. At the end of each transfer, the buffers are swapped so that there is an efficient and continuous image data transfer between the L64702 and external video memory.

On the video port, the chip supports colorspace conversion of three components with nine down-loadable coefficients, which allow any user-defined color-space conversion (RGB to YCrCb, RGB to YUV, etc.). When the L64702 is programmed to handle four components (CYMK), it bypasses the color-space conversion block and generates the proper addressing scheme to convert the raster-ordered image structure in the video memory to block-ordered data required by the L64702 JPEG processing unit. A set of three registers specify the subsampling scheme for each one of the color components.

The L64702 contains integrated DRAM/VRAM controllers with programmable and advanced windowing and addressing mechanisms. Within the programmable active window, the L64702 generates the addresses for the raster-to-block or block-to-raster conversion for a variety of image data structures and subsampling schemes. The L64702 accesses the video memory in master fashion using its own memory controller unit.

The L64702 contains a complete set of control signals that allow direct interface to DRAM/VRAM. The L64702 can be programmed to periodically generate memory refresh cycles. It can also perform periodic screen refresh or image capture functions utilizing the memory-to-shift register or shift register-to-memory transfer cycle. The split read transfer mode is also supported along with regular memory read and write cycles.

The system port is dedicated to compressed data or configuration data transfers. The L64702 operates as a slave peripheral from this port. Memory-mapped data transfers are controlled by an external CPU. DMA data transfers are controlled by an external DMA controller. The system interface port contains all necessary signals to perform handshaking with an external CPU or DMA controller.

The FIFO organization is 32 words by 16 bits. The Code-FIFO buffers data between the JPEG processing unit and the external 16-bit system bus. The

buffering rate can go as high as 40 Mbyte/second. The FIFO also allows burst transfers of compressed data.

Memory-mapped configuration tables and status registers can be accessed by an external CPU via the SRS[1:0] pins in conjunction with an automatically incrementing address pointer. An external DMA controller can access the FIFO or the configuration tables.

The L64702 provides a bypass mode, which allows indirect CPU access of video memory through the L64702 device. This feature allows for easy testing and manipulation of image data in the video memory without any extra hardware needed to provide an interface between the system bus and the video bus. In addition, it allows a low-cost CPU or microcontroller, which may have limited addressing ability, to access up to 64 Mbytes.

### 1.2 Features

This section summarizes the key features of the L64702:

- Implements the proposed baseline JPEG DIS 10918 standard for image compression.

- Supports the detection of restart (RSTn), End Of Image (EOI), and Illegal Marker (IMC) marker codes, byte stripping (during decompression), and byte stuffing (during compression).

- Supports the specification of a compressed file active window structure, allowing small window scrolling in a large compressed file.

- Contains four downloadable quantization tables.

- Contains downloadable Huffman code tables (two DC and two AC tables).

- Supports downloading of all 64 DCT or IDCT coefficients.

- Provides a bypass mode that is capable of transferring original image data to or from memory at a rate of 16.5 Mbytes/second.

- Provides a flexible color-space transformation capability with a down-loadable, 3x3 matrix to allow any linear transformation of three-element vectors.

- Contains a dual-port architecture consisting of a video memory bus interface and an asynchronous system bus interface.

- Includes a multiplexed address and data bus. Supports 24-bit addressing capability allowing direct access up to 16M, 32-bit words.

- Contains an on-chip video memory controller that integrates a programmable active window mechanism and raster-to-block or block-toraster address mechanism.

- Processes data transfer rates of up to 8.25 Mbytes/second during compression or decompression with a 33-MHz external clock. Some of the L64702 image data processing rates supported include:

- 4.125 Mpixels/second for 2:1:1 color (RGB<sub>x</sub>)

- 2.75 Mpixels/second for 1:1:1 color (RGB<sub>x</sub>)

- 8.25 Mpixels/sec for component sequential (CMYK) in any subsampling scheme

- Supports three-component color (for example, RGB) as well as up to four sequential components (for example, CMYK).

- Supports the following color image structures:

- Multiple Sources, RR.....R, GG......G, BB.....B

- Unpacked Color, RGBxRGBx...RGBx

- Packed Color, RGBRGBRG....BRGB

- The components sequential image data structure (up to four components)

- Supports the following image structure subsampling schemes:

- 1:0:0 is used for color to gray scale conversion

- 1:1:1 has no subsampling

- 2:1:1 subsamples components 2 and 3 by factor of two

- Components sequential (four components) at any sampling scheme allowed by the JPEG baseline specification. Both horizontal and vertical subsampling schemes are supported.

- Supports a handshake mechanism for sharing the video bus with other bus master processors.

- Provides direct support for VRAM and DRAM, including all control and refresh signals for five operating schemes:

- read cycle

- write cycle

- <u>CAS</u>-before-<u>RAS</u> refresh cycle

- memory-to-shift register cycle (Split Read and Normal Read Transfers supported)

- shift register-to-memory cycle (Pseudo Write and Alternate Write Transfers supported)

- Provides control signals for flexible multiplexing of row and column addresses and for easy implementation of video banks and interleaved memory structures.

- Supports an asynchronous system interface, which gives the L64702 the capability to operate either as a slave I/O device to an external CPU or as a peripheral device communicating with an external DMA controller.

- Supports 16-bit system bus configurations.

- Includes two external address pins with an internal auto-increment address pointer that implements the memory mapping of all accessible internal resources.

- Includes a programmable threshold for the FIFO, which allows burst code data transfers between the FIFO and system memory.

- Places no restrictions on the data rate from both ports. The JPEG pipeline processing unit can temporarily suspend operation at any time during the process without compromising data integrity.

- Packaged in a 100-pin Plastic Quad Flat Pack (PQFP) package.

- Fabricated using a 0.7 μm, CMOS process with maximum power dissipation of 1.5 watts at 33 MHz.

Introduction 1-7

### 1.3 System Description

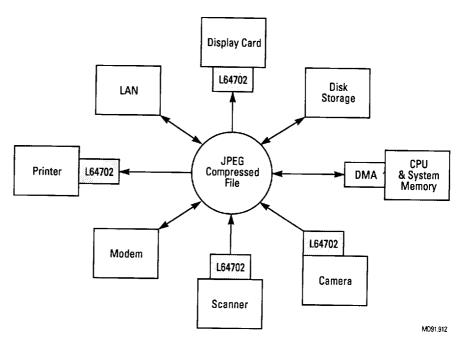

Figure 1.3 File Interchange in a Microcomputer System

Figure 1.3 shows the high-level system approach behind the L64702 device. The chip is designed to serve as either a stand-alone or coprocessor device in each one of the microcomputer peripheral nodes, capable of compressing or decompressing images in various formats.

This section describes the operation of the L64702 in three configurations: coprocessor, stand-alone, and single-bus coprocessor. Coprocessor configurations are used in applications that require both high-speed image compression/decompression and high-speed graphics processing. Stand-alone configurations are intended for systems in which the main system CPU performs the graphics or image processing. Single-bus coprocessor configurations are useful for systems that include printers.

# Coprocessor Configuration

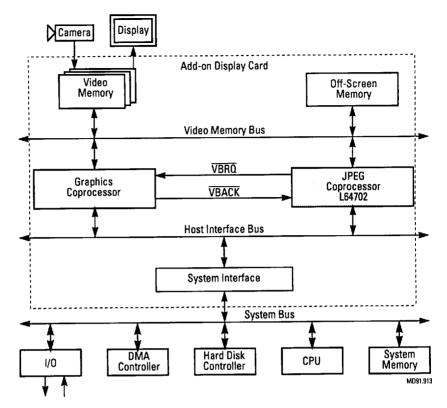

Figure 1.4 shows a basic coprocessor system, which includes the major blocks of a display card design that uses the L64702 JPEG coprocessor and an existing graphic coprocessor. This system configuration applies to high-performance display card applications requiring both high-speed image compression or decompression and high-speed graphics processing. The L64702 improves the processing time when image compression or decompression is needed.

Figure 1.4 Coprocessor System Configuration

The configuration shown in Figure 1.4 is similar to the floating-point coprocessor method used in many microprocessor systems. The system software driver, which monitors both the graphics and JPEG coprocessors, controls the decision to start image compression or decompression, and uses the L64702 to accelerate the operation.

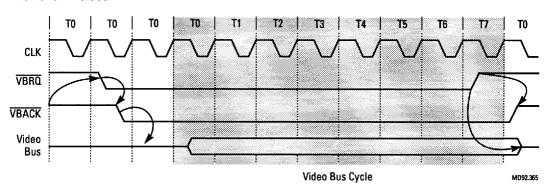

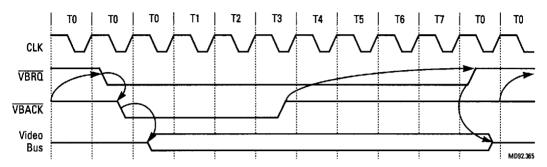

The L64702 interacts with the graphics coprocessor when the L64702 needs the video bus. Both coprocessors can operate concurrently and use the same video bus. The L64702 asserts the  $\overline{VBRQ}$  signal to request video bus mastership. The graphics coprocessor asserts  $\overline{VBACK}$  to acknowledge the request. The L64702 maintains control of the video bus for as long as  $\overline{VBRQ}$  and  $\overline{VBACK}$  are asserted.

To temporarily gain control of the video bus, the graphics coprocessor can deassert VBACK, in which case the L64702 relinquishes the bus immediately. Worst case delay is one video bus cycle (8 CLKs). The L64702 resumes control of the video bus when the graphics coprocessor reasserts VBACK.

## 5304804 0011612 991 **\*\***LLC

The camera and display monitor connect to the video memory serial port. The L64702 is capable of performing both image capture and screen refresh cycles through its video port interface.

The system interface block connects the graphics coprocessor and the L64702 to the system bus. The L64702 system port transfers compressed or configuration data between the L64702 and either the system memory or the system disk. Either a CPU slave access or a DMA service can accomplish this data transfer.

The graphics coprocessor uses the off-screen memory as scratchpad memory for windows applications, video editing, or special effects.

# Stand-Alone Configuration

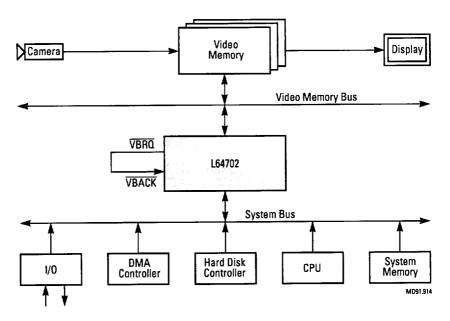

The stand-alone configuration allows the video bus to be completely devoted to the L64702. The  $\overline{VBACK}$  input connects to the  $\overline{VBRQ}$  output. Therefore video bus access is granted to the L64702 upon every  $\overline{VBRQ}$  request.

Figure 1.5 shows a compression/decompression implementation with the L64702 resident on the CPU system bus and used as a coprocessor or hardware accelerator for JPEG image compression and decompression tasks. The CPU can indirectly access the video memory through the L64702. Indirect video memory access allows a CPU with limited addressing capability to address up to 64 Mbytes of DRAM/VRAM.

Image manipulation using the indirect method as portrayed in Figure 1.5 is limited in performance when compared to the graphics coprocessor configuration shown in Figure 1.4. However, for low-cost applications, the indirect method is quite acceptable.

Figure 1.5 Stand-Alone System

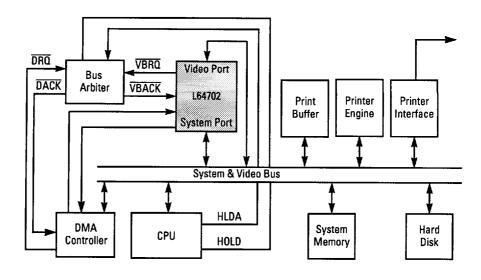

Single-Bus Coprocessor Configuration Figure 1.6 shows the single-bus coprocessor configuration. This configuration is most likely to be implemented in printer systems. The CPU must access the print buffer memory to perform the task of print page making. The L64702 system port and video port both connect to the system bus.

In this configuration, the system bus has three possible master devices: the CPU, the DMA Controller, and the L64702. The CPU, by definition, is the primary master and has the highest priority. The DMA Controller and the L64702 are secondary masters that share the bus in a round-robin arbitration scheme. The advantage of this scheme is that the L64702 system port utilizes an external DMA Controller for compressed image data transfers or device configurations, while the video port acts as a master port sharing the system bus with other bus masters. During image compression or decompression the system bus is shared between DMA transfers of compressed data (performed by the external DMA Controller) and image data transfers (performed by the L64702).

Figure 1.6 Single-Bus Coprocessor Configuration

### 1.4 JPEG Image Compression

When trying to implement multimedia capability in a low cost PC environment, the system designer faces two major problems: limited PC bus bandwidth and storage capacity.

An analog video signal must first be digitized so the computer can process the image data. A typical digitized image contains a huge amount of information. For instance, a 640 x 480 pixel image at 16-bit bits per pixel resolution requires almost 300 Mbytes of storage for only 15 seconds of digital video (at 30 images per second). This size is more than the size of a typical hard disk in a PC system.

Image compression solves this data storage problem. The Joint Photographers Expert Group (JPEG) has created an international standard for image compression. The JPEG standard was originally invented for still image applications, but has proved to be very useful in video applications as well. Using the JPEG algorithm, an image can be compressed 24 to 1 and still retain very good display quality. The image quality can be improved, however, but the higher the image quality, the greater the amount of data storage and bus bandwidth required. At a 24-to-1 compression ratio a user can store more than six minutes of realtime video on a 300 Mbyte hard disk.

The hard disk recording and playback speed may limit the multimedia PC's ability to record and display in realtime. In PCs, the sustained hard disk read or write rate can vary from 150 to 500 Kbytes per second. More expensive hardware, like SCSI disk drives, provide up to 1 Mbyte per second. CDROMs typically have a transfer rate of 300 Kbytes per second.

At a 500 Kbyte per second access rate the video data must be compressed by a factor of almost 40 to 1. This very high compression ratio delivers poor quality image reproduction, so it has become quite common to use quarter screen (320 x 240) size images. A 320 x 240 image requires one fourth the data of a 640 x 480 image, so only a 10 to 1 compression ratio is needed to achieve the data transfer rate of 500 Kbytes per second required for realtime digitization and playback from disk. At an access time of 300 Kbytes per second, a CDROM requires a 15-to-1 compression ratio.

LSI Logic's L64702 JPEG Coprocessor provides programmable compression ratios with the ability to process up to 8.25 Mbytes of pixel data per second.

JPEG also allows compatibility among the various image standards found in desktop multimedia systems containing cameras, copiers, and scanners. Although each produces or displays images in different ways and in conformance with different standards, JPEG allows for intercommunication among all of them.

### 1.5 Standards Compliance

The L64702 conforms to these international standards:

- CCIR Recommendation 601 (Mod F), Encoding Parameters of Digital Television for Studios

- JPEG DIS 10918, Digital Compression and Coding of Continuoustone Still Images

The compliance of the L64702 with each of these standards is discussed below.

### CCIR 601 (Mod F)

The CCIR Recommendation 601 presents a proposed standard for color space conversions. CCIR 601 specifies the conversion between R, G, B and Y, Cr, Cb; and other aspects of color conversions. The L64702 internal Color Converter complies with CCIR 601 (Mod F).

### **JPEG DIS 10918**

The Joint Photographic Experts Group (JPEG) is proposing an international standard for the compression and decompression of still photographic images. LSI Logic designed the L64702 internal DCT Processor and JPEG Coder to comply with JPEG DIS 10918.

Introduction 1-13

In the terminology of the JPEG standard, the L64702 supports baseline sequential DCT-based Huffman coding for eight-bit source images. The L64702 also supports interleaved data containing up to four components.

### 1.6 Terms and Concepts

This section explains some important terms and concepts used in the rest of this guide. The subsections are:

- Minimum Coded Unit (MCU)

- MCU Boundaries

- Display Active Image Area

- Compressed Image Active Window

- Color Conversion

- Subsampling

- Image Reconstruction

- Raster-to-Block Conversion

- DCT Functions

- Quantization Function

- Zigzag Ordering

- DPCM Coding

- Run-Length Coding

- Variable-Length Coding (Huffman Coding)

- Encoding Example

# Minimum Coded Unit (MCU)

The JPEG DIS 10918 standard specifies the concept of a minimum coded unit (MCU). An MCU is a sequence of data units (8 x 8 blocks) defined by the sampling factors of the image components. The L64702 supports a wide variety of sampling factors. The sampling factor determines the size of the MCU.

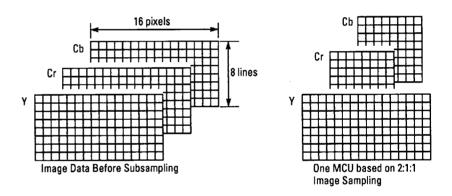

When the L64702 operates in the color mode and color space conversion is used, three color components are supported (for example, RGB or YCrCb). The color space conversion is completely programmable, allowing any number of color conversion possibilities. Three sampling factors are used to define the MCUs. The sampling factors are 1:0:0, 1:1:1, or

2:1:1. A sampling factor of 1:0:0 indicates that an MCU is constructed from one 8 x 8 block of the first color component only. A sampling factor of 1:1:1 indicates that an MCU is constructed from one 8 x 8 block from each color component.

When an image consists of the YCrCb color components, for example, and 2:1:1 sampling is implemented, each MCU contains two 8 x 8 data blocks of the *luminance* (intensity) component, Y, and one 8 x 8 data block each of the two *chrominance* (color) components, Cr and Cb.

With 2:1:1 sampling, the MCU is constructed from an image area of 16 pixels wide by eight lines high. Every pixel of the Y component is included in the sample, but only every other pixel of the Cr and Cb components is included. The resulting MCU consists of four 8 x 8 blocks—two Y blocks, one Cr block and one Cb block.

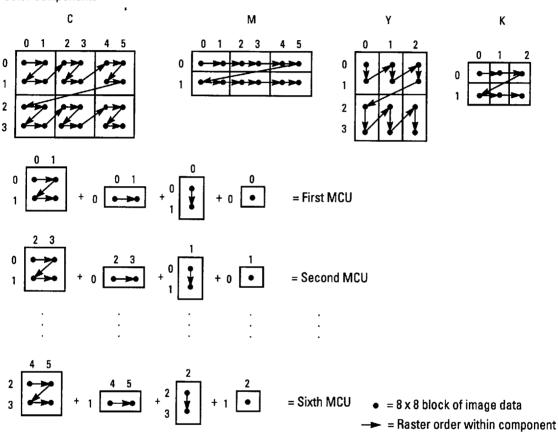

Figure 1.7 shows how an MCU is constructed with 2:1:1 subsampling.

Figure 1.7

Construction of an

MCU from Three

Color Components

When the L64702 operates in the components sequential mode, it does not perform color space conversion, and supports up to four color components. The L64702 is compatible with any sampling factor specified by the baseline JPEG standard.

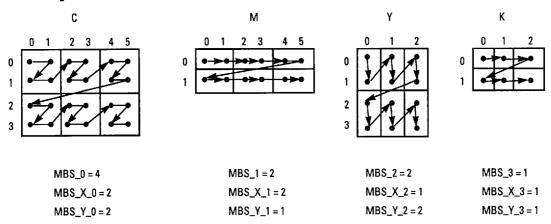

Figure 1.8 illustrates how an MCU is constructed from a four-color image. The sampling ratio is 4:2:2:1, which means that the MCU is constructed from four 8 x 8 blocks of the C component, two blocks of the M component, two blocks of Y and one block of K. Registers in the L64702 allow the construction of an MCU to be completely described, in terms of how many blocks are assembled from each color component, and the vertical and horizontal ordering in which the assembly takes place. Each MCU

contains a total of 9 8 x 8 blocks (4 + 2 + 2 + 1). Each dot in the figure represents an 8 x 8 block of image data.

Figure 1.8

Construction of an

MCU from Four

Color Components

The MCU is constructed from an image area 16 pixels wide by 16 lines high (four 8 x 8 blocks). Every pixel of the C component is included in the sample, but only every other pixel of the M and Y components is included, and every fourth pixel of the K component.

The components of an image are subsampled *prior* to image compression, and the L64702 assumes that the components are stored in the memory in four separate regions.

The first MCU is constructed of 8 x 8 blocks taken first from the top left-most region of the C color component (four blocks), followed by two blocks from the same region of the M component, then from Y, and finally from K. The second MCU is constructed following the same ordering for data taken from the next region to the right for the four components. This same procedure is followed for constructing all six MCUs.

### MCU Boundaries

If the image size is such that the edge of the image does not fall on an MCU boundary, the L64702 fills the remainder of the MCU with zeroes to make sure that all compressed data consists of complete MCUs.

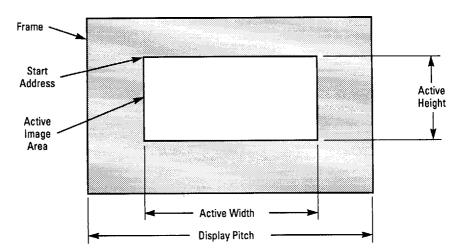

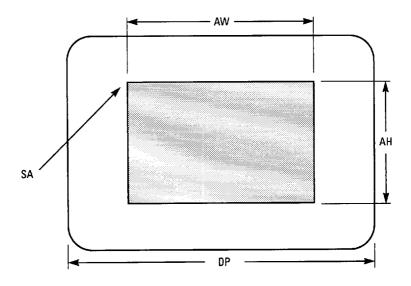

### Display Active Image Area

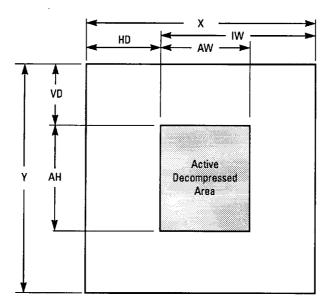

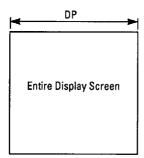

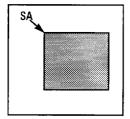

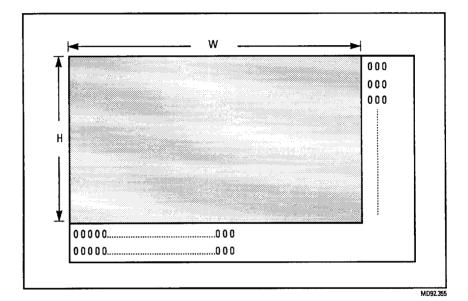

In many applications, only a portion of the source image stored in video memory is processed. This portion of the image is known as the *active image area*. The active image area is defined in terms of parameters written by the CPU to the L64702 internal registers. These parameters are: *start address, active height, active width*, and *display pitch*.

Figure 1.9 shows the definition of these parameters relative to the complete image. The start address defines the location in video memory where the active image begins. The active height, active width, and display pitch are measured in MCUs and provide the L64702 with information on the size of the active window relative to the rest of the display area. The shaded portion of the frame is outside of the active image area and is ignored by the L64702. Data in the shaded region is not accessed by the L64702 during image compression or decompression.

Figure 1.9 Active Image Area

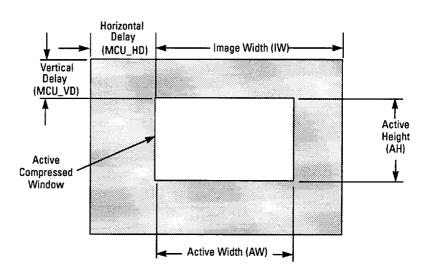

### Compressed Image Active Window

A special feature of the L64702 allows an active window to be defined within a compressed file. The compressed file represents the entire image. However, a portion of the image can be defined as active so that when the L64702 operates in the decompression direction, it displays only the active portion. An active window display capability is useful if you wish to preview or scroll and display only a portion of a very large image that will not fit on the display screen. Figure 1.10 shows the active window in a compressed file.

Two additional parameters, horizontal delay (MCU\_HD) and vertical delay (MCH\_VD), are provided in addition to those shown in the Active Image area of Figure 1.9. These parameters tell the L64702 how many MCUs to skip in the compressed file before starting to decompress.

Figure 1.10 Compressed Image Active Window

#### **Color Conversion**

The L64702 is capable of flexible color space conversion. The RGB-to-YCrCb and YCrCb-to-RGB color conversions are defined in CCIR 601. Any set of 3 x 3 matrix coefficients may be downloaded into the L64702, providing an extremely flexible color space conversion system. The L64702 supports any linear transformation of a 3 x 1 vector by multiplying it by the downloaded 3 x 3 matrix.

As an example, the first set of equations below shows how the L64702 operates on RGB image data to transform RGB data to YCrCb data. The RGB-to-YCrCb color conversion is shown as a series of linear equations

and also as a matrix equation. The second set of equations shows how the same procedure is used for the YCbCr-to-RGB color conversion. RGB and Y values are in the range 16-235 inclusive; Cr and Cb values are in the range 16-240 inclusive. The actual coefficients that are used in the matrix range from 1.998 to -2.000.

With this flexible arrangement, the L64702 supports other conversions, such as RGB-to-Y and Y-to-RGB. By setting up the 3 x 3 conversion matrix as a unit matrix, the color space conversion may be altogether bypassed.

Equation 1.1 RGB to YCrCb Conversion

$$\begin{bmatrix} Y \\ Cr \\ Cb \end{bmatrix} = \begin{bmatrix} 0.299 & 0.587 & 0.114 \\ 0.5 & -0.419 & -0.081 \\ -0.169 & -0.331 & 0.5 \end{bmatrix} \times \begin{bmatrix} R \\ G \\ B \end{bmatrix}$$

Equation 1.2 YCrCb to RGB Conversion

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \begin{bmatrix} 1.0 & 1.402 & 0 \\ 1.0 & -0.7143 & -0.3437 \\ 1.0 & 0.0 & 1.772 \end{bmatrix} \times \begin{bmatrix} Y \\ Cr \\ Cb \end{bmatrix}$$

### Subsampling

When the Color Space Converter is used in the encoding direction, the L64702 can *subsample*. Subsampling is a process in which data is sampled periodically, for example, every other pixel. See the subsection entitled "Minimum Coded Unit (MCU)" on page 1-14, along with Figure 1.7 for an explanation of 2:1:1 subsampling performed by the L64702.

The image subsampling operation reduces the number of pixels of one color component relative to another. The subsampling process is a way of accomplishing up-front video image compression besides the regular compression scheme involving quantization. The basic principle underlying subsampling is that there is some redundancy in color components. This redundancy can be eliminated by subsampling in such a way that the image quality is not impacted. The best known subsampling scheme is the 4:2:2 YCrCb format. This scheme samples the Y component in the color subcarrier four times for every two times that the Cr and Cb components are each sampled. Twice as many Y pixels are produced as either Cr or Cb pixels.

In a JPEG system, the Y, Cr, and Cb components that result from subsampling are interleaved and transferred as 8 x 8 blocks. The 4:2:2 format is translated to 2:1:1 JPEG subsampling, which means that there are two 8 x 8 blocks of Y followed by one 8 x 8 block of Cr and one 8 x 8 block of

Cb. These four blocks are also called an MCU. To construct this particular MCU, an area of 16 pixels by 8 lines is needed.

Refer to Section 7.4, "Image Subsampling," for more information.

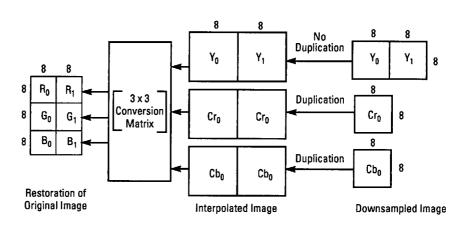

### Image Reconstruction

When the Color Space Converter is used in the decoding direction to decode 2:1:1 coded images, the chrominance components (Cr and Cb) are replicated. Each block of 8 x 8 pixels for a given chrominance component is expanded into a 16 x 8 block. The additional 64 values, which were earlier eliminated by downsampling during encoding, are interpolated based on the current chrominance values. In fact, the additional 64 values are duplicates of the current chrominance values. Since none of the luminance pixels (Y) were eliminated by downsampling, there is no need to interpolate missing pixels for that part of the image. Figure 1.11 illustrates the process of image reconstruction.

Figure 1.11 Image Reconstruction from YCrCb to RGB

## Raster-to-Block Conversion

The L64702 converts the full-image raster data into data blocks of eight pixels by eight pixels, the format used by the DCT Processor and the JPEG Coder.

In the encoding direction, the L64702 reads the first eight pixels of the video memory in the horizontal direction, then reads the next eight pixels of the next display line, and so on, until an image area eight pixels by eight pixels is read. The eight pixels of each line are read in *raster order*; that is, from left to right. The resulting array is an 8 x 8 block, thus fulfilling the *raster-to-block* conversion requirement. The next raster-to-block conversion starts back on the first display line, on the ninth pixel from the

beginning. Thus the L64702 reads through the video memory and prepares a sequence of 8 x 8 blocks in the order described. Figure 1.12 illustrates raster-to-block conversion.

In the decoding direction, the L64702 reads 8 x 8 blocks and performs a block-to-raster conversion. The block-to-raster conversion takes pixels from each 8 x 8 block and writes an 8 x 8 area in video memory (eight pixels wide by eight lines high).

Figure 1.12 Raster-to-Block Conversion

### **DCT Functions**

The DCT Processor performs the *forward* (FDCT) and *inverse discrete* cosine transforms (IDCT). The purpose of FDCT and IDCT is to transform image data between the time domain and the frequency domain.

In video compression, the FDCT function is implemented first, followed by quantization. In video decompression, inverse quantization occurs first, followed by the IDCT function. IDCT performance meets the CCITT requirements. The DCT/IDCT coefficients may be downloaded into the L64702. The equations for these transforms are shown below. The symbols used in the equations are defined following the equations.

Equation 1.3 Forward DCT

$$F_{v, u} = \frac{1}{4} C_u C_v \sum_{x=0}^{7} \sum_{y=0}^{7} f_{y, x} \cos \frac{(2x+1) u\pi}{16} \cos \frac{(2y+1) v\pi}{16}$$

(FDCT)

Equation 1.4 Inverse DCT

$$f_{y,x} = \frac{1}{4} \sum_{u=0}^{7} \sum_{v=0}^{7} C_u C_v F_{v,u} \cos \frac{(2x+1)u\pi}{16} \cos \frac{(2y+1)v\pi}{16}$$

(IDCT)

where:

u = horizontal frequency index

v = vertical frequency index

x = horizontal position index

y = vertical position index

$$C_u$$

,  $C_v = \frac{1}{\sqrt{2}}$  for  $u, v = 0$   $C_u$ ,  $C_v = 1$  otherwise

The L64702 calculates the DCT or IDCT coefficients in two separate matrix operations as follows:

$$[\overline{Y}] = [A] \bullet [X]$$

$$[Y] = [A] \bullet [\overline{Y}]^{\mathsf{T}}$$

where:

[A] is the 8 x 8 DCT or IDCT matrix.

[X] is the 8 x 8 input data matrix to the FDCT/IDCT L64702 block.

$[\overline{Y}]$  is the result of the first operation.

[Y] is the final result.

#### Quantization Function

Quantization categorizes data into discrete values. Quantization is a lossy process, meaning that information is lost in the quantization process.

The forward and inverse *quantization functions* performed by the JPEG Coder are shown below. The data used in the quantization is stored within the L64702 in four *quantization tables*. The symbols used are defined following the equations.

Equation 1.5 Forward Quantization

$$Q(x(i), i) = round(\frac{x(i)}{q(i)})$$

Equation 1.6 Inverse Quantization

$$x'(i) = Q(x(i), i) \cdot q(i)$$

where:

x(i) = DCT coefficient created by the DCT Processor.

- x'(i) = reconstructed DCT coefficient created by the quantizer in the L64702. Since quantization is a lossy process, x'(i) is not necessarily equal to x(i).

- Q(x(i), i) =quantized DCT coefficient. Q(x(i), i) is the output of the quantizer and the input to the coding modules when the L64702 is in DCT encoding configuration. Q(x(i), i) is the output of the decoding modules and the input to the inverse quantizer when the L64702 is in DCT decoding configuration.

- q(i) = quantization stepsize from the quantization table for the component being quantized.

- round(x) = rounding function. round(x) rounds to the nearest integer. When x is halfway between two integers, round(x) rounds up for positive and down for negative values of x.

- i = index of the DCT or reconstructed DCT coefficient. i is in the range from 0 to 63 inclusive.

Figure 1.13 shows the forward and inverse quantization functions. Empty circles indicate that the endpoint of the line segment is not included.

Table 1.1 shows examples of a forward and inverse quantization of several input values. The table assumes that source data is first quantized, then reconstructed using the same quantization stepsize q. Note that in general, the reconstructed value differs from the source value.

Table 1.1 Quantization Examples

| Source<br>Data | Quantized<br>Data | Reconstructed<br>Data |

|----------------|-------------------|-----------------------|

| 1.2q           | 1                 | 1q                    |

| -0.4q          | 0                 | 0                     |

| 3.0q           | 3                 | 3q                    |

Figure 1.14 shows an example of forward quantization on an input signal with three non-zero values. The input function and the quantization function are shown on the upper graph, and the resulting quantized function is shown on the lower graph.

Figure 1.14 Quantization Example

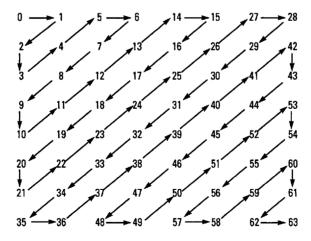

#### Zigzag Ordering

The DCT processor encodes DCT coefficients and outputs the data in either raster order or, more commonly, zigzag order. Zigzag ordering orders the coefficients in increasing order of frequencies, which creates longer runs of zero values and increases coding efficiency in the JPEG Coder.

Figure 1.15 shows zigzag ordering. The figure shows the rearrangement of the block from raster order. Coefficient 0 is the DC coefficient and coefficients 1 through 63 are AC coefficients, with the lower frequencies having the lower-numbered coefficients.

Figure 1.15 Zigzag Ordering

| 0  | 1  | 5  | 6  | 14 | 15 | 27 | 28 |

|----|----|----|----|----|----|----|----|

| 2  | 4  | 7  | 13 | 16 | 26 | 29 | 42 |

| 3  | 8  | 12 | 17 | 25 | 30 | 41 | 43 |

| 9  | 11 | 18 | 24 | 31 | 40 | 44 | 53 |

| 10 | 19 | 23 | 32 | 39 | 45 | 52 | 54 |

| 20 | 22 | 33 | 38 | 46 | 51 | 55 | 60 |

| 21 | 34 | 37 | 47 | 50 | 56 | 59 | 61 |

| 35 | 36 | 48 | 49 | 57 | 58 | 62 | 63 |

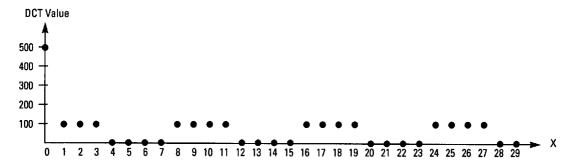

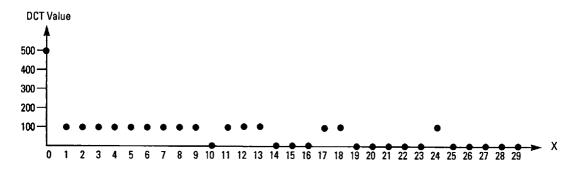

Figure 1.16 shows an example of the benefits of zigzag ordering. The data block shows a typical distribution of DCT coefficients. The graphs below the data block show the runs for raster and zigzag ordering. Notice that zigzag ordering concentrates the non-zero coefficients and in general produces longer zero-length runs.

Figure 1.16 Raster and Zigzag Encoding Example

| 0  | 500 | 100 | 100 | 100 | 0 | 0 | 0 | 0 |

|----|-----|-----|-----|-----|---|---|---|---|

| 8  | 100 | 100 | 100 | 100 | 0 | 0 | 0 | 0 |

| 16 | 100 | 100 | 100 | 100 | 0 | 0 | 0 | 0 |

| 24 | 100 | 100 | 100 | 100 | 0 | 0 | 0 | 0 |

|    | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 |

|    | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 |

|    | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 |

|    | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 |

Raster Order

Zigzag Order

#### **DPCM Coding**

Each DC coefficient is coded using the DC coefficient value for the previous block of the same component as a predictor. This coding scheme is called differential pulse-code modulation (DPCM). The difference between the current DC coefficient and the previous value is coded. The previous value of the DC coefficient is stored in one of four internal DC predictor registers (one for each component). When the L64702 is reset, the internal DC predictor values are set to zero. The DPCM coding in the L64702 conforms to the proposed JPEG DIS 10918 standard for encoding DC coefficients in sequential DCT-based processes.

The equation for the DPCM is shown below.  $\Delta(n)$  is the predictor that is coded at the start point of the coding operation DC<sub>-1</sub> = 0 so  $\Delta(0)$  = DC<sub>0</sub>.

### Equation 1.7 DPCM Coding

$$\Delta(n) = DC_n - DC_{n-1}$$

#### Run-Length Coding

The AC coefficients are first coded by a *run-length coding* algorithm. In run-length coding, each AC coefficient is coded as an event consisting of a run of zero coefficients and a non-zero value. (DC coefficients always have a zero run length, since the DC coefficient is the first coefficient in the block.) The run-length coding in the JPEG Coder conforms to the proposed JPEG standard<sup>1</sup> for encoding AC coefficients in sequential DCT-based processes.

#### Variable-Length Coding (Huffman Coding)

The code preprocessor and code tables generate *variable-length code-words* or *Huffman codes*. The codewords are chosen to maximize compression for the image data type to be processed. The most commonly occurring events are assigned the shortest codewords. See the proposed JPEG standard for more information about creating code tables.

<sup>1.</sup> The International Standard Draft is expected to be approved as an international standard shortly.

# Encoding Example

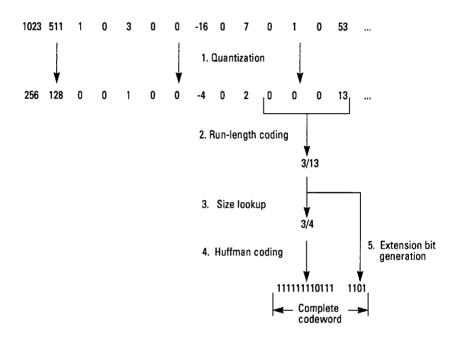

The following example shows the JPEG Coder's operation in DCT-based encoder configuration. Figure 1.17 and the explanations following the figure show how a portion of an input data stream is encoded.

Figure 1.17

Encoding Example

#### Quantization

Quantization reduces the number of data values and increases the number of zeros. In this example, all values in the quantization table are assumed to be four. The quantized values are determined by the forward quantization function described earlier in the subsection entitled "Quantization Function." For example, the DCT coefficient 53 in the input stream is quantized as shown below:

Equation 1.8 DCT Coefficient Calculation

$$Q(x(i), i) = round(\frac{53}{4}) = round(13.25) = 13$$

#### **Run-Length Coding**

The run-length coder determines the number of zeros between successive non-zero coefficients. In the indicated portion of the data stream, three zeros precede the non-zero coefficient 13.

#### Size Lookup

The code preprocessor looks up the size corresponding to the coefficient in the size table shown in Table 1.2. In the example, the coefficient 13 corresponds to the size 4.

Table 1.2 AC Coefficient Size Table

| Size | AC Coefficient   |

|------|------------------|

| 1    | -1,1             |

| 2    | -3,-2,2,3        |

| 3    | -74,47           |

| 4    | -158,815         |

| 5    | -3116,1631       |

| 6    | -6332,3263       |

| 7    | -12764,64127     |

| 8    | -255128,128255   |

| 9    | -511256,256511   |

| 10   | -1023512,5121023 |

#### **Huffman Coding**

The variable-length coder uses the run and size values to look up the Huffman code in the code table. The code tables are set up by the user as described in Chapter 3, "Internal Registers and Data Tables." Table 1.3 shows a portion of the code table used in this example. The entry used in the example is shown in bold.

Table 1.3 Sample AC Code Table

| Run/Size | Huffman Code      |

|----------|-------------------|

|          | •                 |

| •        | •                 |

| 3/2      | 11111000          |

| 3/3      | 1111111000        |

| 3/4      | 111111110111      |

| 3/5      | 1111111110010001  |

| 3/6      | 11111111110010010 |

| •        |                   |

|          | •                 |

#### **Extension Bit Generation**

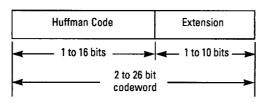

The code preprocessor determines the extension bits using the algorithm given in the following paragraphs and shown in Figure 1.18.

C is the coefficient in two's complement notation, and S is the size. If C is greater than zero, the extension bits are the S low-order bits of C. If C is less than zero, the extension bits are the S low-order bits of (C-1).

In this example, C is equal to 13 (binary code  $000.0000.1101_2$ ) and S is equal to four. The extension bits are the four low-order bits  $1101_2$ .

Figure 1.18 shows the general structure of the codewords generated by the L64702.

Figure 1.18 Codeword Structure

## 1.7 Applications

This section lists the typical applications for the L64702:

- Multimedia

- Image transmission systems, modems, color faxes, and LANs

- Image storage and retrieval systems

- Display cards

- Color and gray-scale printers, copiers, and scanners

- Color publishing and pre-press systems

- Digital cameras

# Chapter 2 Interface Description