CL450

MPEG

VIDEO

DECODER

USER'S

MANUAL

# CL450 MPEG Video Decoder User's Manual

C-Cube Microsystems reserves the right to change any products described herein at any time and without notice. C-Cube Microsystems assumes no responsibility or liability arising from the use of the products described herein, except as expressly agreed to in writing by C-Cube Microsystems. The use and purchase of this product does not convey a licence under any patent rights, copyrights, trademark rights, or any other intellectual property rights of C-Cube Microsystems.

# **Trademark Acknowledgment:**

C-Cube and CL450 are trademarks of C-Cube Microsystems.

The corporate logo is a registered trademark of C-Cube Microsystems.

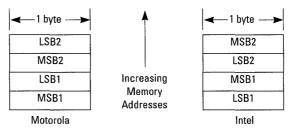

Motorola is a registered trademark of Motorola, Inc.

Intel is a registered trademark of Intel Corporation.

© C-Cube Microsystems 1994 All rights reserved

> C-Cube Microsystems 1778 McCarthy Boulevard Milpitas, CA 95035 Telephone (408) 944-6300 Fax (408) 944-6314

### **Customer Comments and Feedback:**

If you have any comments about this document, send them to the C-Cube Technical Publications Department at the address listed above, or send e-mail to:

techpubs@c-cube.com

C-Cube Part # 90-1450-101

# **Preface**

This manual is the primary source of technical information for the operation and programming of the C-Cube CL450 MPEG Video Decoder.

#### This manual is intended for:

- □ System designers and managers who are evaluating the CL450 for possible use in a system.

- Design, software and system engineers developing a video decoding system using the CL450 for whom a comprehensive programming background as well as a detailed understanding of MPEG compression is assumed.

In particular, readers should understand the MPEG standard: *Coded Representation of Picture*, *Audio and Multimedia/Hypermedia Information*, ISO/IEC JTC 1/SC 29, December 6, 1991.

As an aid to developing systems and applications based on the CL450, readers may also wish to obtain C-Cube's CL450 MPEG Video Decoder Sample Kit, which includes a sample development board, microcode and user's guide.

#### This manual is divided into three main sections:

- □ Section I, General Information, including an introduction to the CL450 and the MPEG standard that it implements.

- □ Section II, Hardware Interface, including signal descriptions, operational information for the main interfaces of the CL450, registers, and detailed electrical and mechanical specifications.

# **Audience**

# Related Publications

# Organization

□ Section III, Software Interface, including an overview of the fundamental mechanisms used to communicate between the host system and the CL450's microapplication, and an alphabetical listing of all macro commands and interrupts available to the programmer. Note: the microapplication information in this manual applies to CL450 versions 2.00 through 2.FF *only*.

# **Conventions**

Please note the following notation examples and conventions used in this manual:

| Notation                                                 | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Examples                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x1c3                                                    | "0x" prefix indicates a hexadecimal number.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11011 <sub>2</sub>                                       | "2" subscript indicates a binary number.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IMEM                                                     | Four-letter mnemonics indicate on-chip memories, starting with a letter to indicate function of memory, and ending with "MEM." For example, IMEM is the CL450's instruction memory.                                                                                                                                                                                                                                                                                   |

| HOST_control<br>CMEM_control                             | This format indicates a register name. The first part of a register name is a group specifier, given in all upper-case. The second part (separated from the first by an underscore and given in all lower-case) is a register specifier, indicating the function performed by the register within the group. In the examples shown, HOST_control and CMEM_control are separate registers, even though both have the same register specifier, "control."               |

| VIE, Res                                                 | Italicized acronyms or abbreviations (initial or all caps) indicate bit field names within registers or data words.                                                                                                                                                                                                                                                                                                                                                   |

| HMEM[3]<br>CPU_control[0]<br>HMEM[0][15]<br>HMEM[3][2:0] | Square bracket notation similar to C language array subscripting indicates words within memories, and bits within words and registers. HMEM[3], for example, is the 16-bit word at address 3 within HMEM, while CPU_control[0] is bit 0 of the CPU_control register. Similarly, HMEM[0][15] is the most significant bit of the word at HMEM address 0.                                                                                                                |

|                                                          | Ranges of bits are indicated by numbers separated by a colon such as the three bits HMEM[3][2:0]. Ranges of words within a memory are indicated by numbers separated by a dash such as the eight words HMEM[0-7].                                                                                                                                                                                                                                                     |

| RESERVED or<br>Res                                       | Indicates bit fields within registers which are not defined. RESERVED bit fields may return any value when read and must be written with 0 (or 1 if so specified). Writing the incorrect value to a RESERVED CL450 register bit will cause indeterminate behavior. In addition, all CL450 registers which are not explicitly given names are also RESERVED, and accessing these registers may cause indeterminate results on current or future CL450 implementations. |

| leftBorder                                               | Bold-face type represents macro command arguments.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| return();                                                | C-style syntax presented in courier typeface represents program pseudocode and equations.                                                                                                                                                                                                                                                                                                                                                                             |

| vbv_delay                                                | Names presented in courier represent names of items within the MPEG bit-<br>stream taken from the MPEG standard.                                                                                                                                                                                                                                                                                                                                                      |

In some cases, this current reference scheme departs from the method used by the first edition

of the CL450 MPEG Video Decoder User's Manual which, for example, referred to CMEM as both

the "Coded Data FIFO" and "C-FIFO."

# **Contents**

# **Section I. General Information**

| 1 | Intr | oduction                          |     |

|---|------|-----------------------------------|-----|

|   | 1.1  | General Description               | 1-1 |

|   | 1.2  | The CL450 Product Family          | 1-1 |

|   |      | 1.2.1 CL450 Features              | 1-2 |

|   |      | 1.2.2 Microapplication Features   | 1-3 |

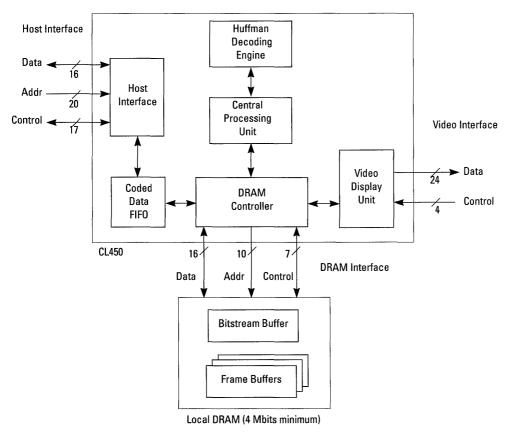

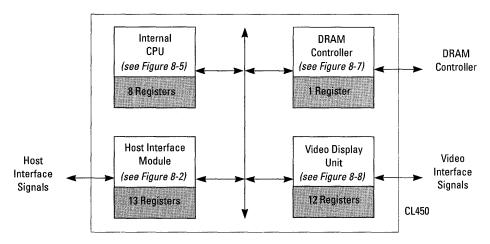

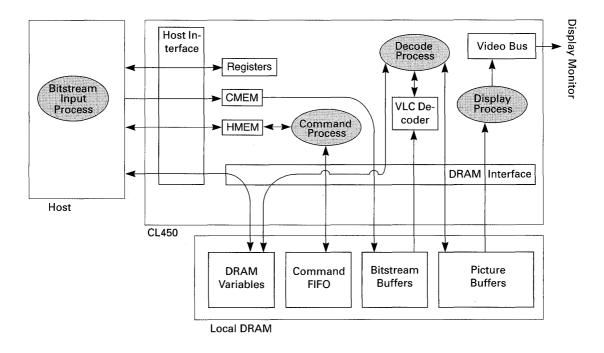

|   | 1.3  | Functional Description            | 1-4 |

|   | 1.4  | Data Organization                 | 1-5 |

|   |      | 1.4.1 CL450 Registers             | 1-5 |

|   |      | 1.4.2 CL450 Memories              | 1-6 |

|   | 1.5  | Address Size                      | 1-6 |

|   | 1.6  | Programming Overview              | 1-7 |

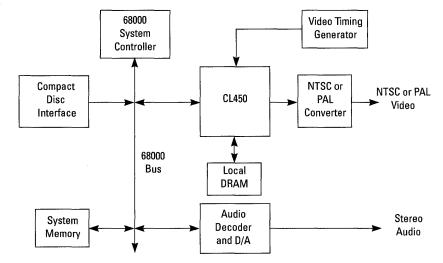

|   | 1.7  | Typical Applications              | 1-8 |

| 2 | MF   | PEG Overview                      |     |

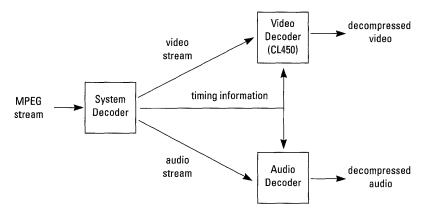

|   | 2.1  | MPEG Decoding                     | 2-2 |

|   |      | 2.1.1 MPEG Stream Structure       | 2-2 |

|   |      | 2.1.2 General Decoding Process    | 2-2 |

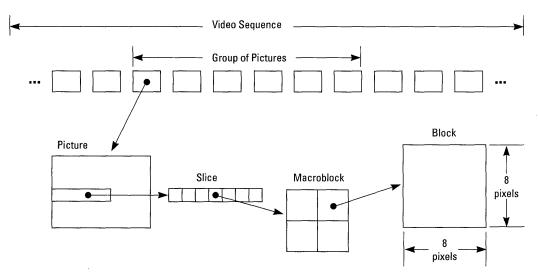

|   |      | 2.1.3 Video Stream Data Hierarchy | 2-3 |

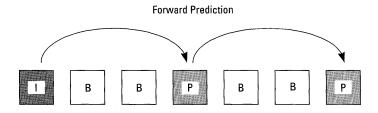

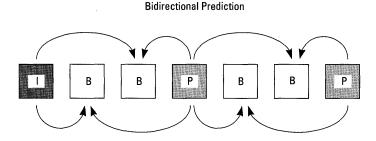

| 2.2   | Inter-picture Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-6  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

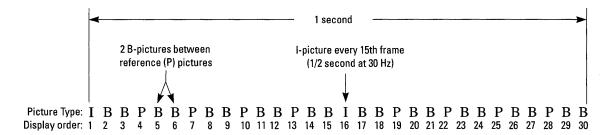

|       | 2.2.1 Picture Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-6  |

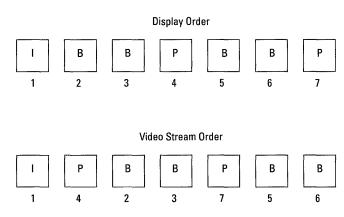

|       | 2.2.2 Video Stream Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-7  |

|       | 2.2.3 Motion Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-8  |

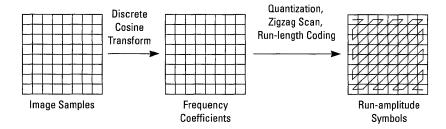

| 2.3   | Intra-picture (Transform) Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-10 |

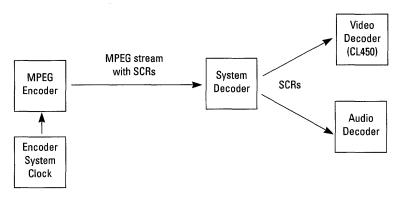

| 2.4   | Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-11 |

|       | 2.4.1 System Clock References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-11 |

|       | 2.4.2 Presentation Time Stamps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-12 |

|       | Section II. Hardware Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

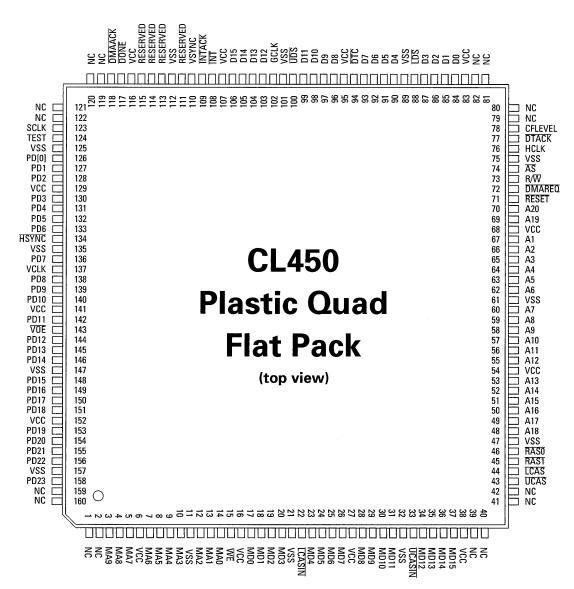

| 3 Sig | gnal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

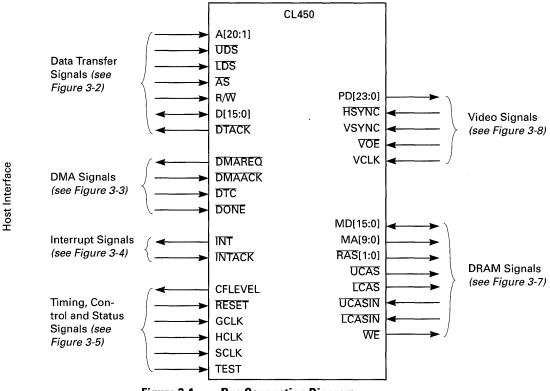

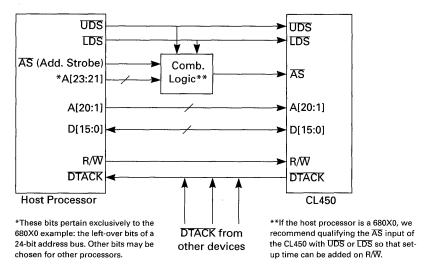

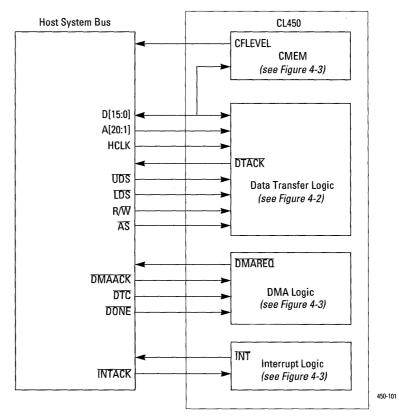

| 3.1   | Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-2  |

|       | 3.1.1 Data Transfer Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-3  |

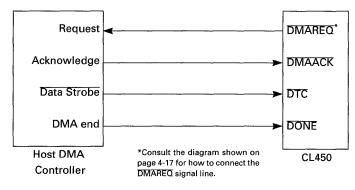

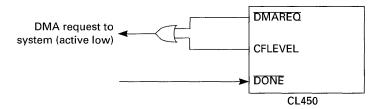

|       | 3.1.2 DMA Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-5  |

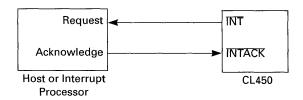

|       | 3.1.3 Interrupt Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-6  |

|       | 3.1.4 Timing, Control, and Status Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-7  |

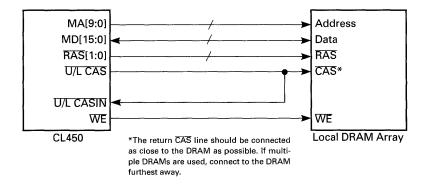

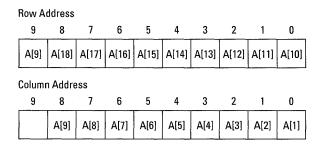

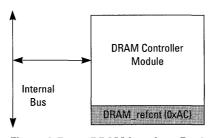

| 3.2   | DRAM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-10 |

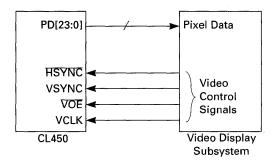

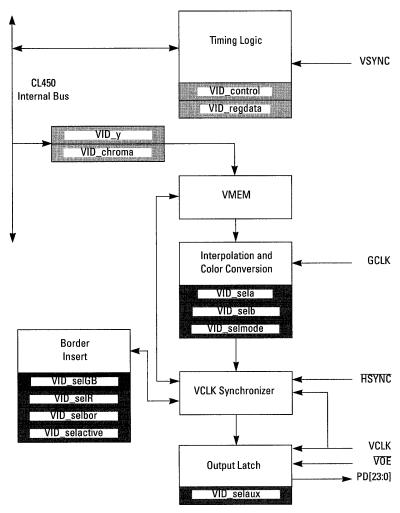

| 3.3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-11 |

| 3.4   | Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-13 |

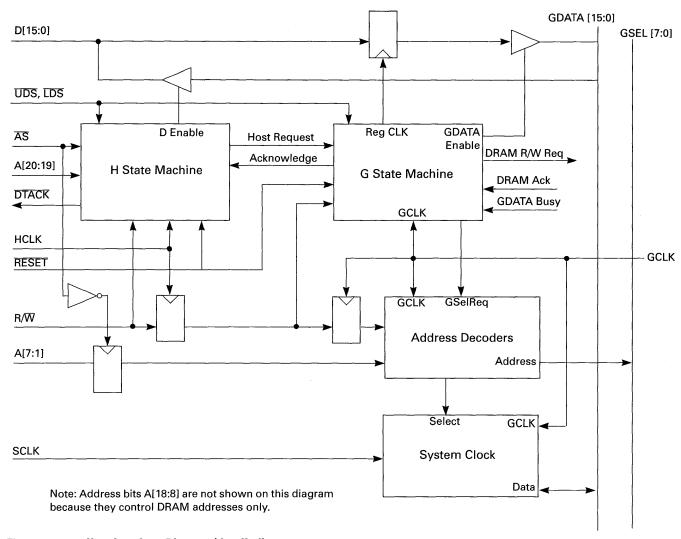

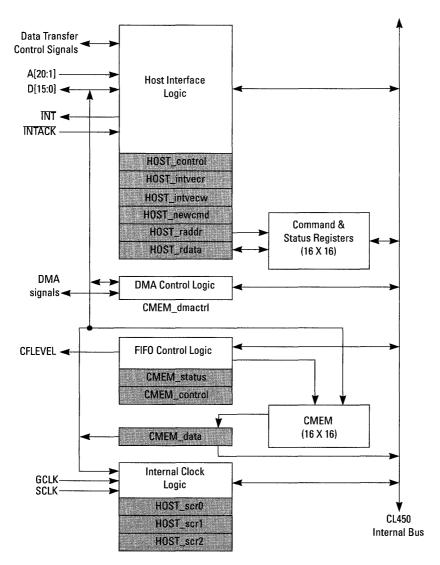

| 4 Ho  | st Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •    |

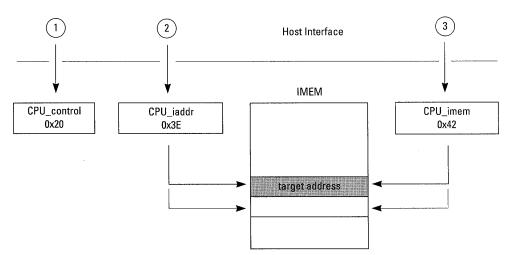

| 4.1   | Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-2  |

|       | 4.1.1 Register Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-4  |

|       | 4.1.2 Local DRAM Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-4  |

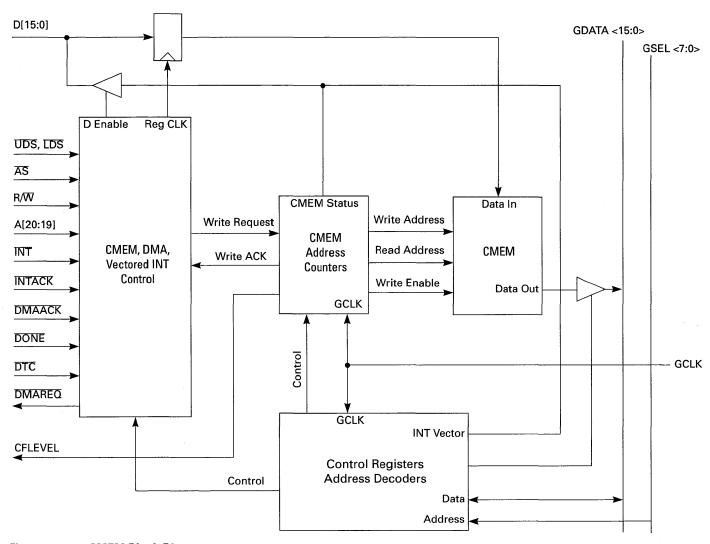

|       | 4.1.3 CMEM Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-6  |

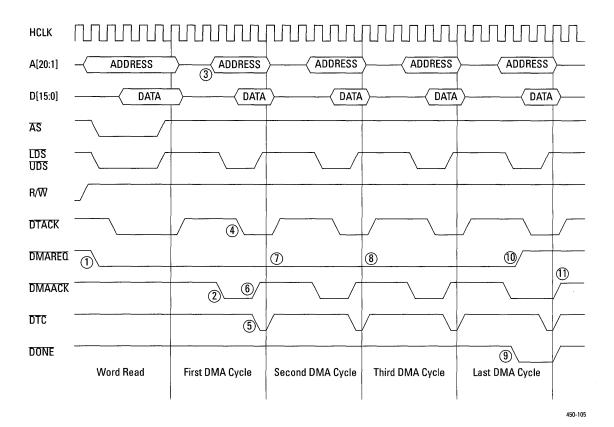

|       | 4.1.4 DMA Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-6  |

|       | 4.1.5 Interrupt Vector Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-6  |

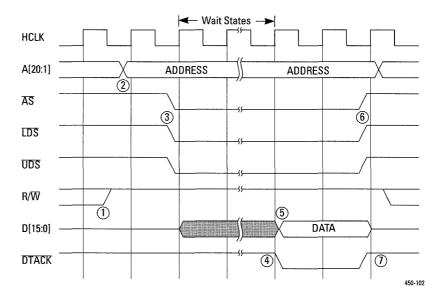

| 4.2   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-8  |

| 4.3   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-9  |

| 4.4   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-11 |

| 4.5   | J The state of the | 4-14 |

| 4.6   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-16 |

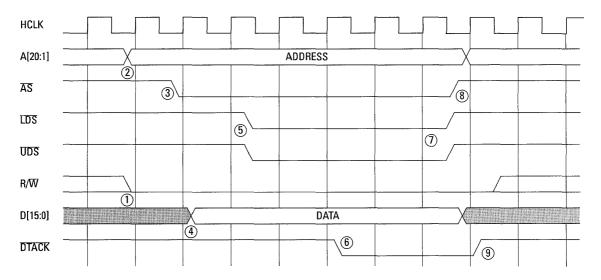

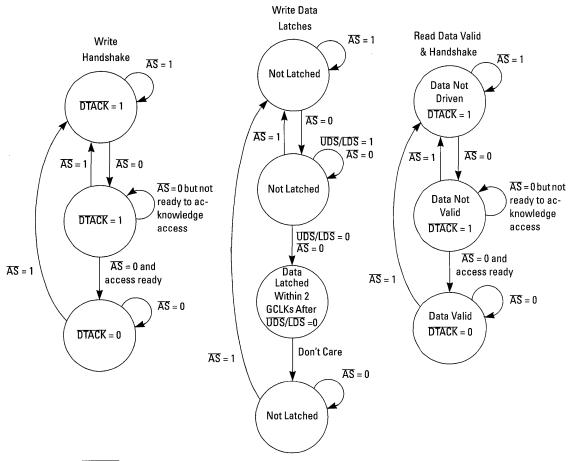

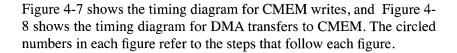

| 4.7   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-18 |

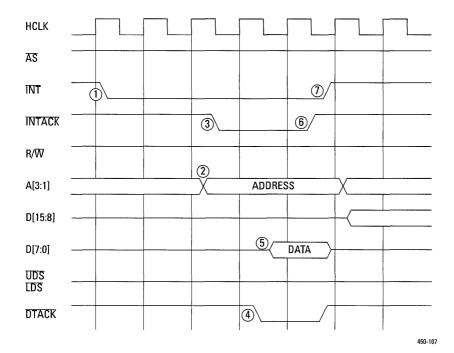

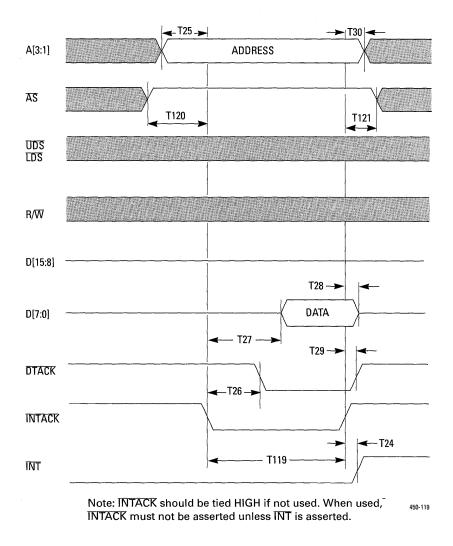

| 4.8   | Interrupt Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-19 |